# SOS Radiation Hard

# Hi-Rel IC and ASIC Handbook

#### **DATASHEET ANNOTATION**

GPS annotate datasheets in the top right hand corner of the first page, to indicate product status. These annotations are as follows:

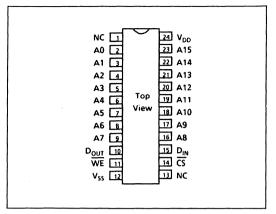

#### TARGET SPECIFICATION

This is the most tentative form of information and represents a very preliminary product specification. No actual design work on the product has started.

#### PRELIMINARY INFORMATION

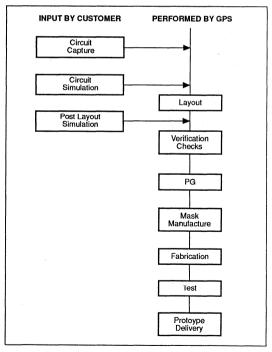

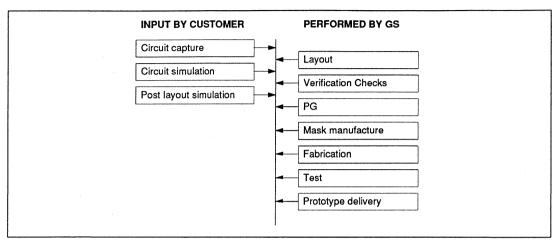

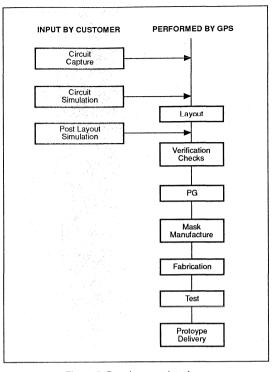

The product is in design and development. The datasheet represents the product as it is understood but details may change.

#### **ADVANCE INFORMATION**

The product design is complete and final characterisation for volume production is well in hand.

#### No annotation

The product parameters are fixed and the product is available to datasheet specification in volume.

If you have any queries about the status of any GPS product, please contact your nearest GPS Customer Service Centre.

# SOS Radiation Hard

Hi-Rel IC and ASIC Handbook

# Contents

|             |                                                        | Page |

|-------------|--------------------------------------------------------|------|

|             | Product List                                           | 4    |

|             | GPS Space & Radiation Hard Products Technical Helpline | 5    |

|             | Hardware & Software Support for MIL-STD-1750 Products  | 6    |

|             | Introduction                                           | 8    |

| Section 1:  | Microprocessors                                        | 15   |

| Section 2:  | Peripherals & Support Circuits                         | 237  |

| Section 3:  | Bit Slice & Arithmetic Circuits                        | 423  |

| Section 4:  | Memories                                               | 461  |

| Section 5:  | Databus Products                                       | 583  |

| Section 6:  | Logic                                                  | 789  |

| Section 7:  | Semicustom ASICs & Foundry Service                     | 909  |

| Section 8:  | Bipolar Devices                                        | 933  |

| Section 9:  | Manufacturing Capability Document                      | 947  |

| Section 10: | <b>GPS Locations</b>                                   | 979  |

# **Product List**

| Type No.               | Microprocessors                                             | Page |

|------------------------|-------------------------------------------------------------|------|

| MA31750                | HIGH PERFORMANCE MIL-STD-1750 MICROPROCESSOR                | 17   |

| MA31750 - APPS NOTE 2  | MIL-STD-1750B FEATURES                                      | 59   |

| MA31750 - APPS NOTE 3  | FURTHER USE OF CONSOLE MODE                                 | 60   |

| MA31750 - APPS NOTE 4  | INTERRUPT OPERATIONS                                        | 64   |

| MA31750 - APPS NOTE 8  | USE OF VIO INSTRUCTION                                      | 69   |

| MA31750 - APPS NOTE 11 | BUS ARBITER                                                 | 71   |

| MA31750 - APPS NOTE 14 | USE OF NMA31750 SAMPLES                                     | 76   |

| MA31750 - APPS NOTE 15 | PIPELINING INSTRUCTIONS ON THE MA31750                      | 77   |

| MA31750SBC             | SINGLE BOARD COMPUTER                                       | 78   |

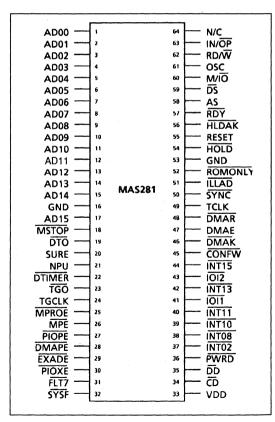

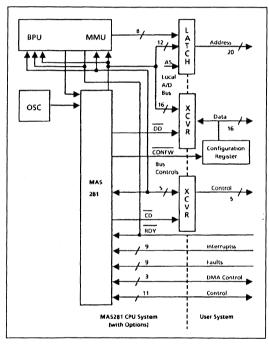

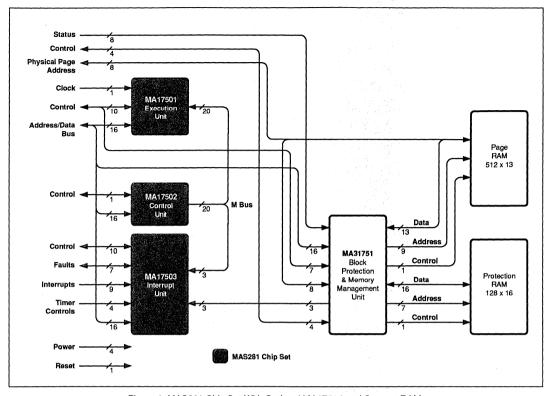

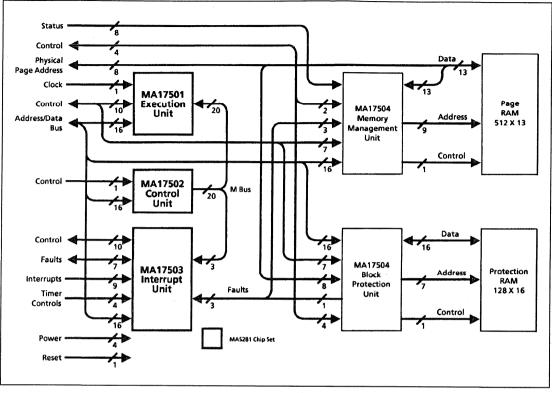

| MAS281                 | MIL-STD-1750A MICROPROCESSOR                                | 86   |

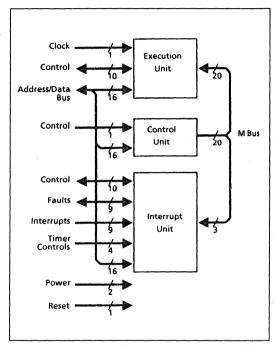

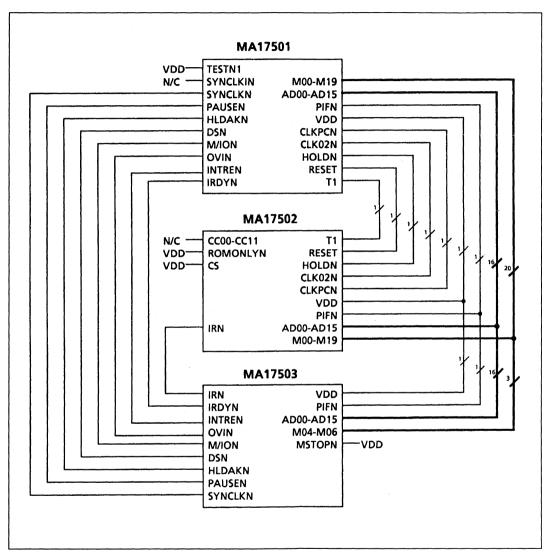

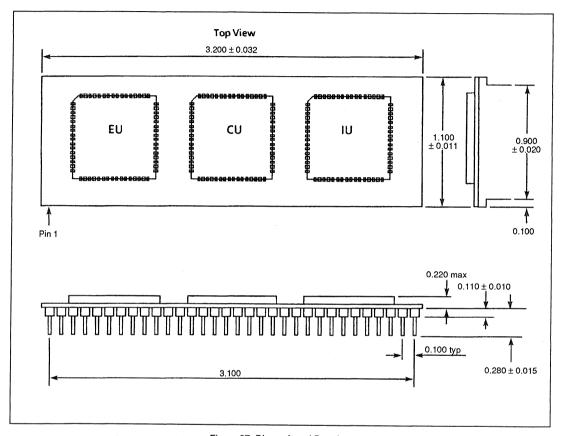

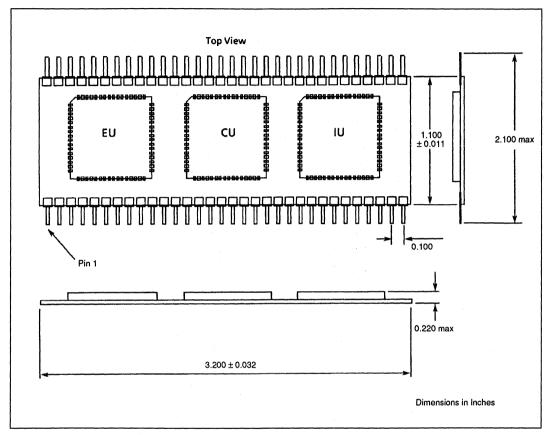

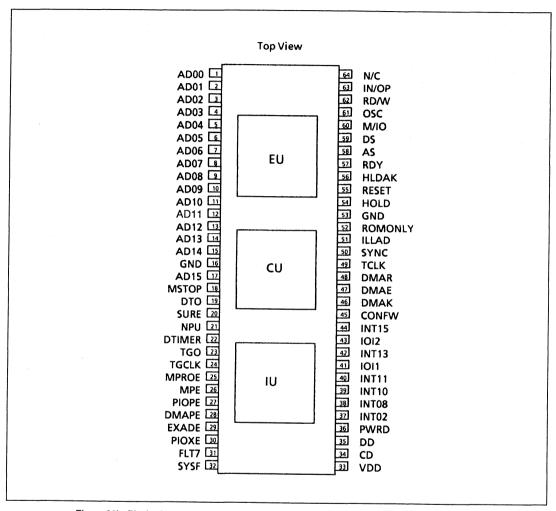

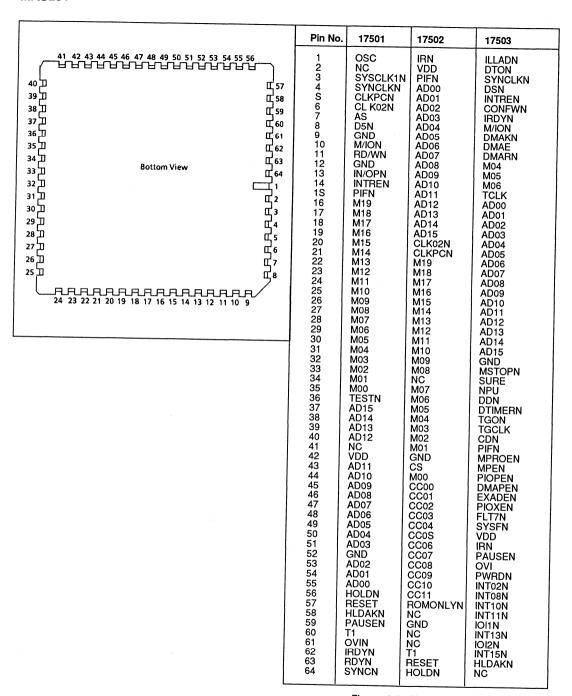

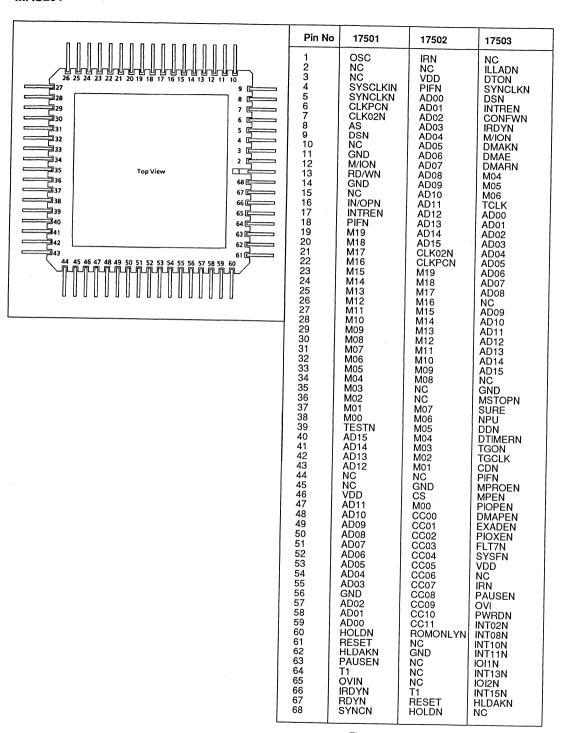

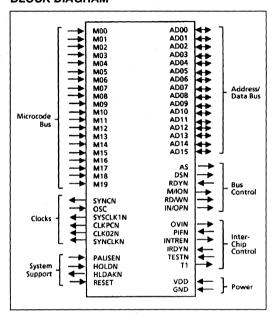

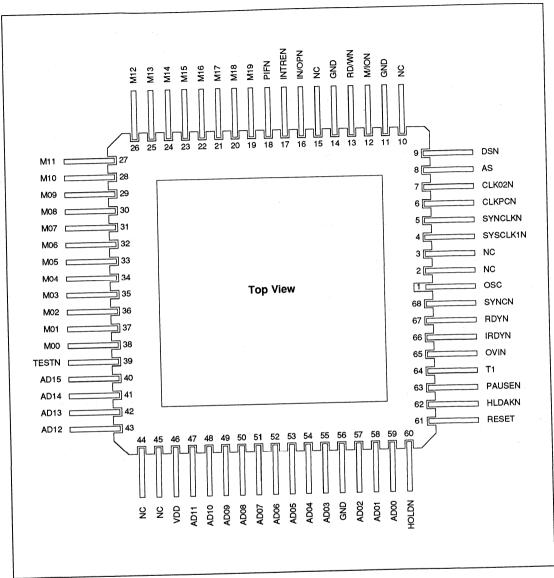

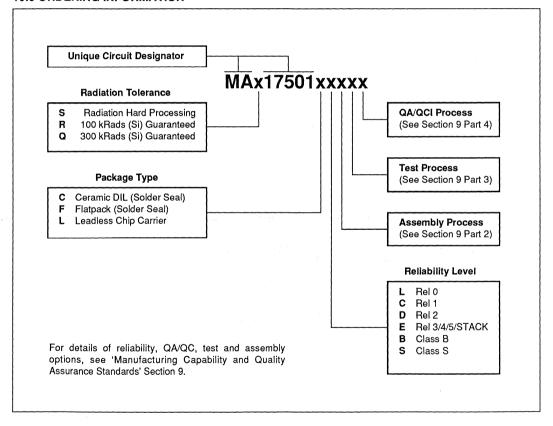

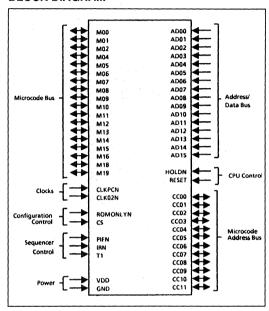

| MA17501                | MIL-STD-1750A EXECUTION UNIT                                | 141  |

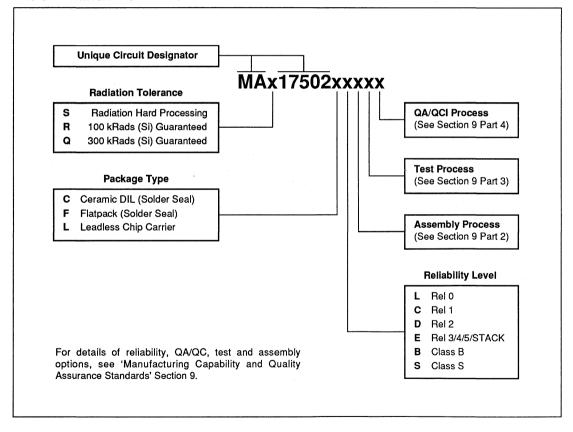

| MA17502                | MIL-STD-1750A CONTROL UNIT                                  | 175  |

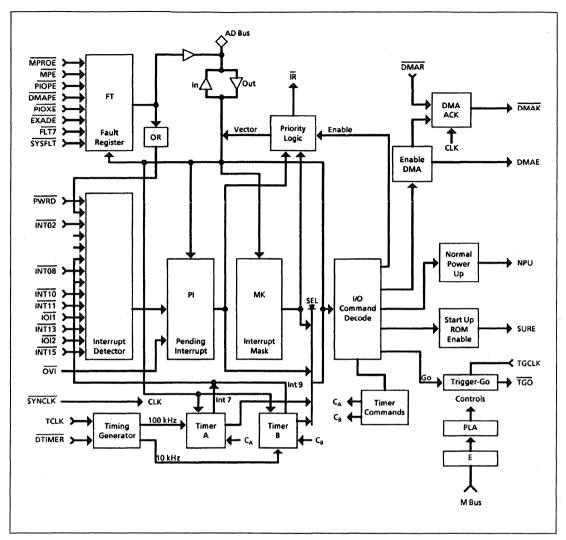

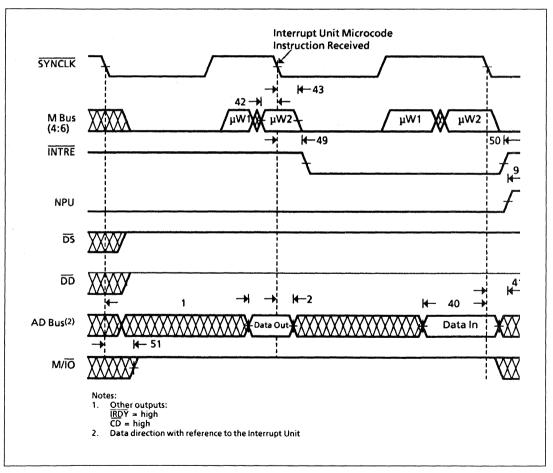

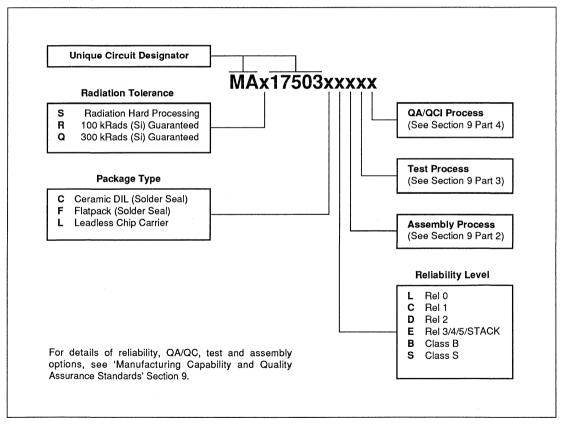

| MA17503                | MIL-STD-1750A INTERRUPT UNIT                                | 204  |

|                        | Peripherals & Support Circuits                              |      |

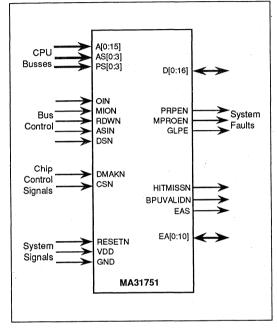

| MA31751                | MEMORY MANAGEMENT UNIT & BLOCK PROTECTION UNIT              | 239  |

| MA31751 - APPS NOTE 5  | DETAILED DEVICE DESCRIPTION                                 | 256  |

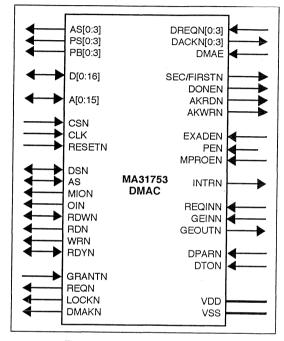

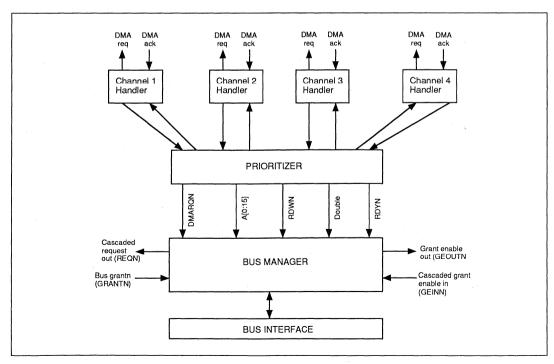

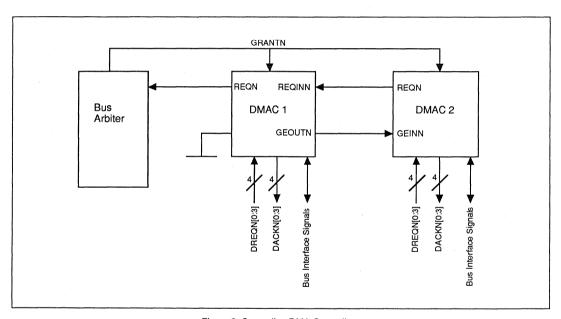

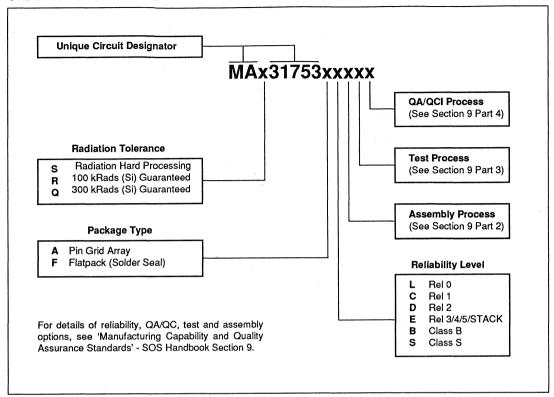

| MA31753                | DMA CONTROLLER (DMAC) FOR USE IN AN MA31750 SYSTEM          | 264  |

| MA31754                | PERIPHERAL SUPPORT CHIP (PSC)                               | 294  |

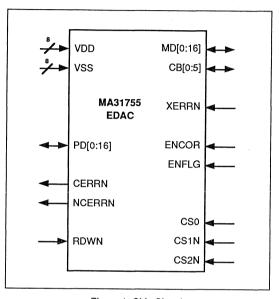

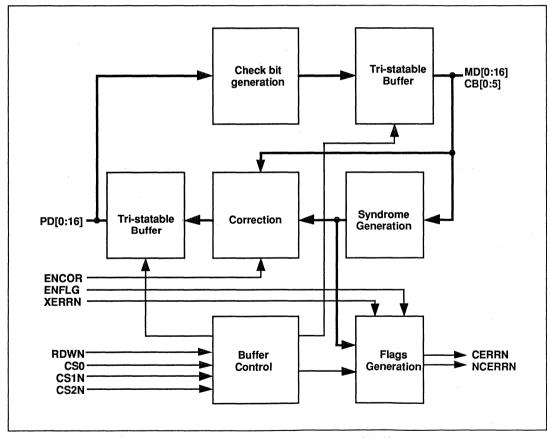

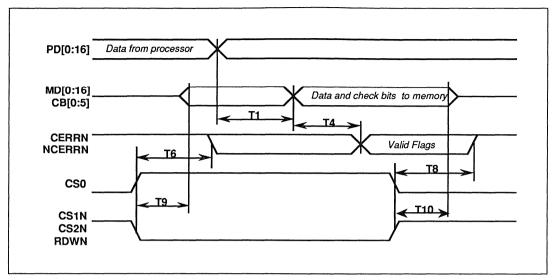

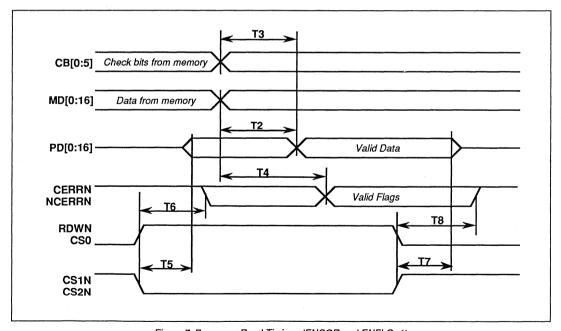

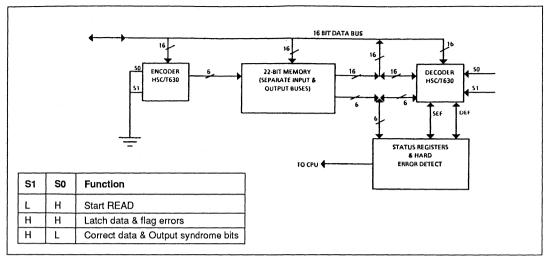

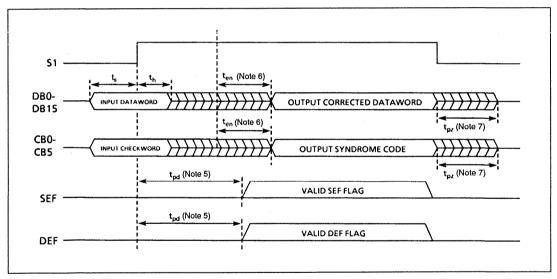

| MA31755                | 16-BIT FEEDTHROUGH ERROR DETECTION & CORRECTION UNIT (EDAC) | 318  |

| MA31755 - APPS NOTE 1  | EDAC ALGORITHMS ON THE MA31752 & MA31755                    | 330  |

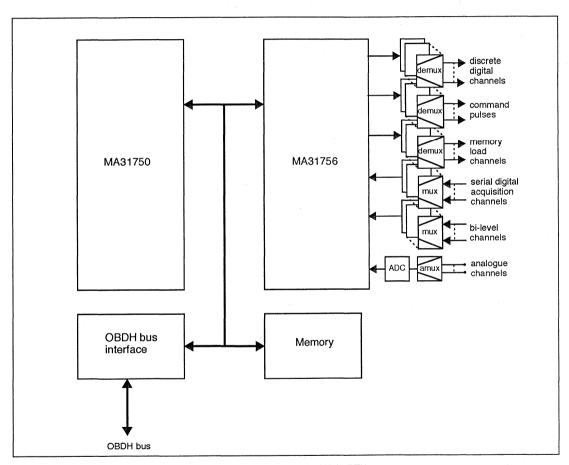

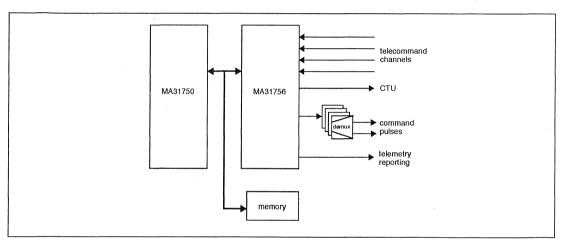

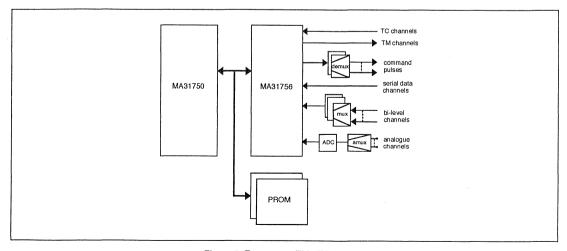

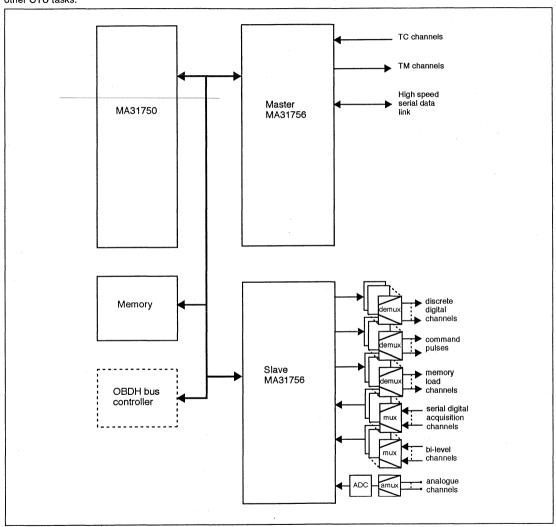

| MA31756                | SINGLE CHIP PERIPHERAL CONTROLLER FOR THE MA31750           | 332  |

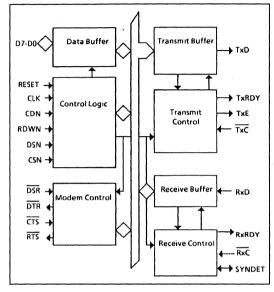

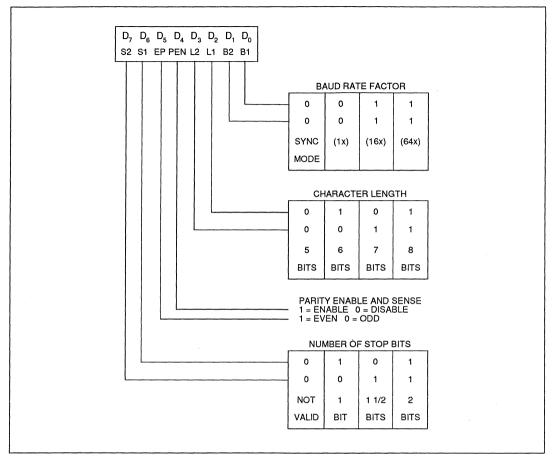

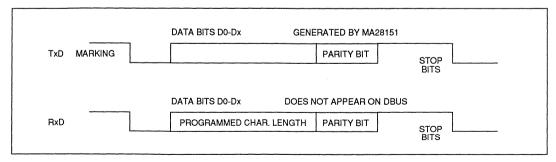

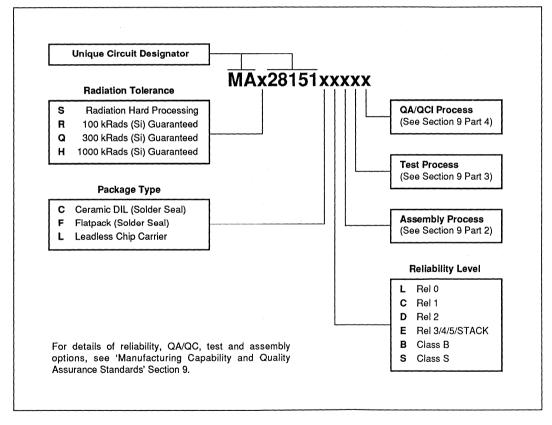

| MA28151                | PROGRAMMABLE COMMUNICATION INTERFACE                        | 343  |

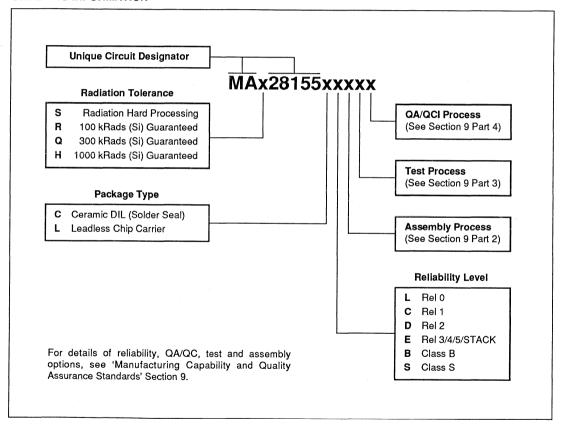

| MA28155                | PROGRAMMABLE PERIPHERAL INTERFACE                           | 364  |

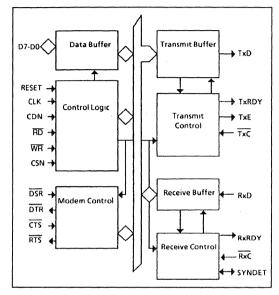

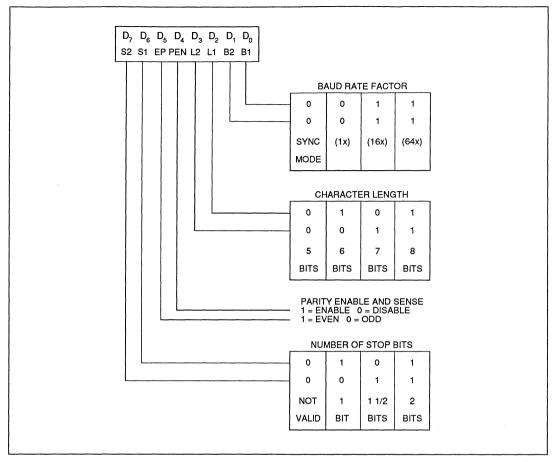

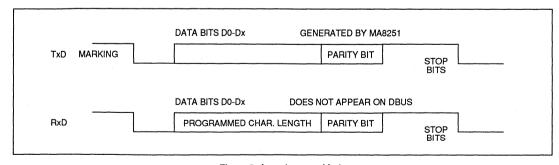

| MA8251                 | PROGRAMMABLE COMMUNICATION INTERFACE                        | 383  |

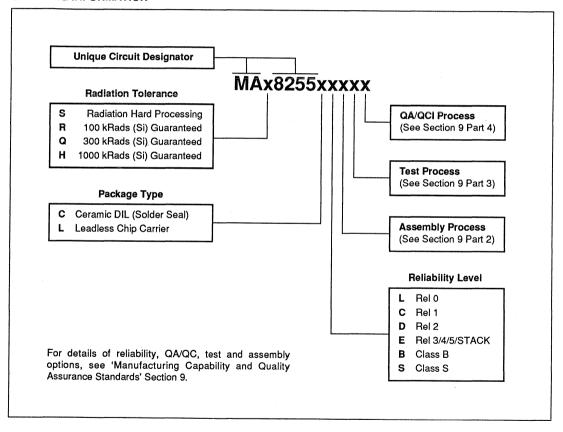

| MA8255                 | PROGRAMMABLE PERIPHERAL INTERFACE                           | 404  |

|                        | Bit Slice & Arithmetic Circuits                             |      |

| MA2901                 | 4-BIT MICROPROCESSOR SLICE                                  | 425  |

| MA2909/11              | MICROPROGRAM SEQUENCER                                      | 436  |

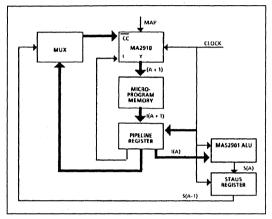

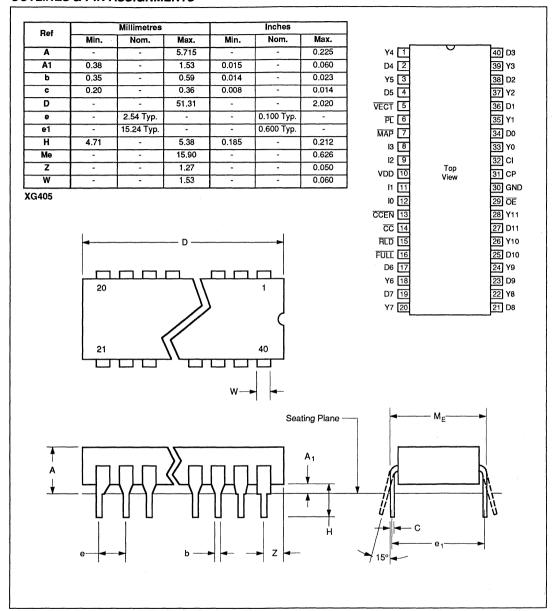

| MA2910                 | MICROPROGRAM CONTROLLER                                     | 447  |

|                        | Memories                                                    |      |

|                        | OVERVIEW OF THE GPS 1.5μm CMOS/SOS SRAM RANGE               | 463  |

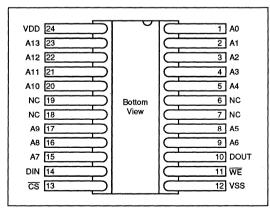

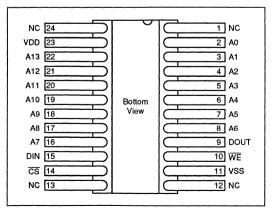

| MA5104                 | 4096 x 1-BIT STATIC RAM                                     | 465  |

| MA5114                 | 1024 x 4-BIT STATIC RAM                                     | 476  |

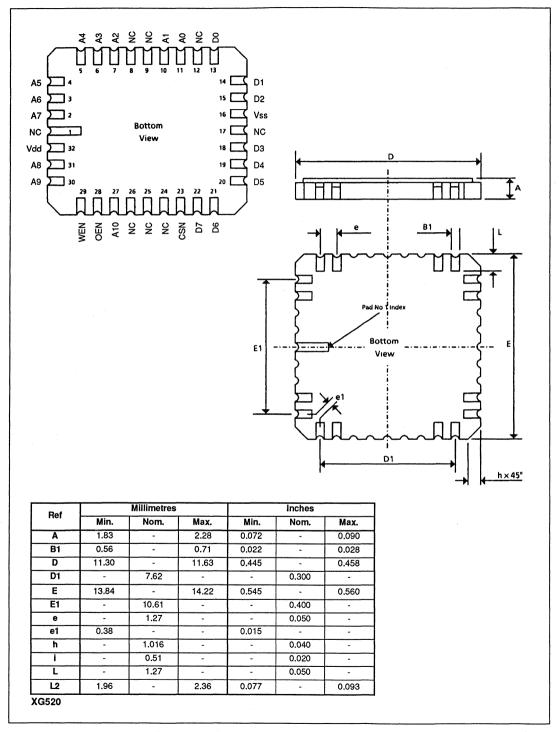

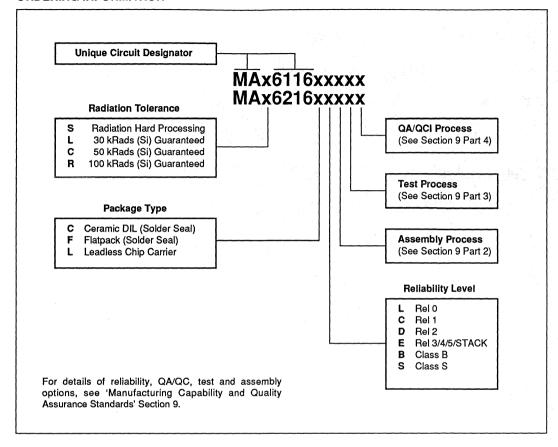

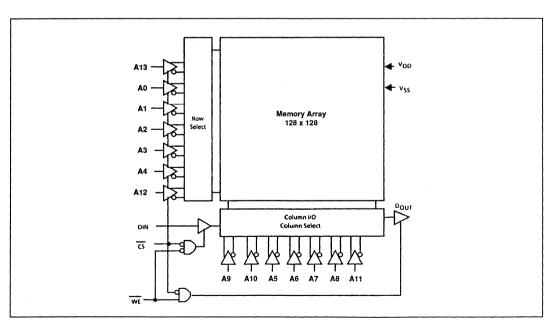

| MA6116/6216            | 2048 x 8-BIT STATIC RAM                                     | 488  |

| MA9167                 | 16384 x 1-BIT STATIC RAM                                    | 500  |

| MA9187                 | 65536 x 1-BIT STATIC RAM                                    | 515  |

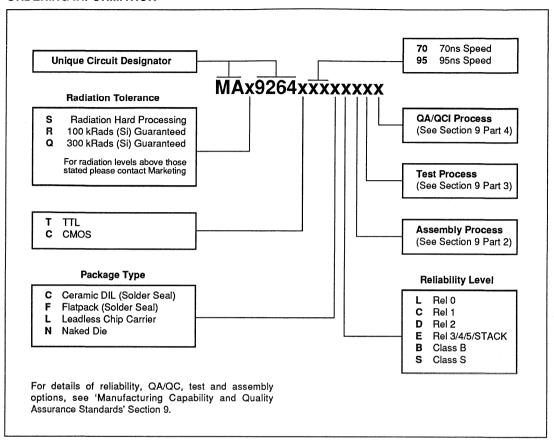

| MA9264                 | 8192 x 8-BIT STATIC RAM                                     | 530  |

| MA9564                 | HIGH TRANSIENT 8192 x 8-BIT STATIC RAM                      | 545  |

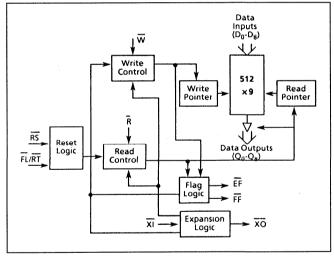

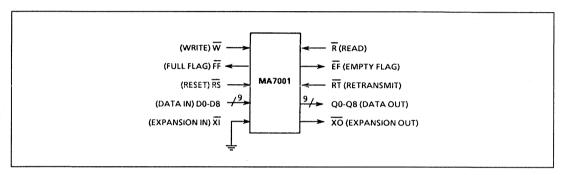

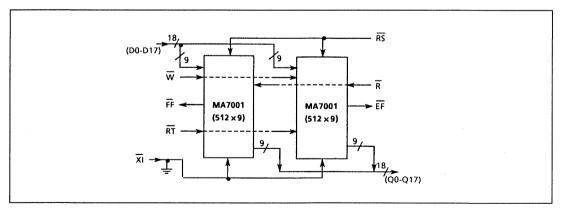

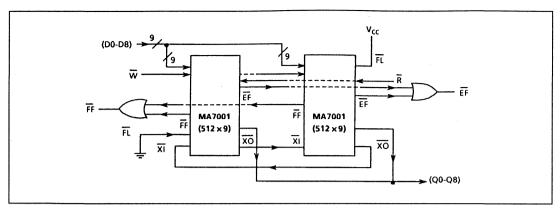

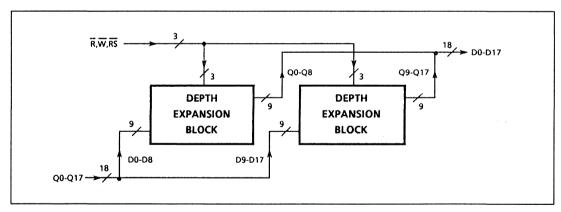

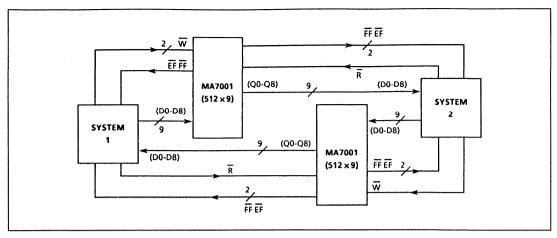

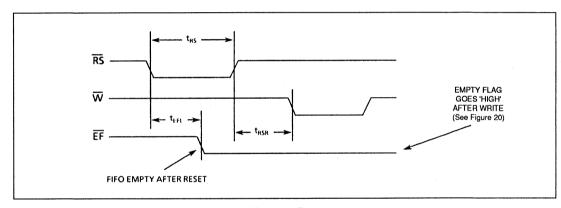

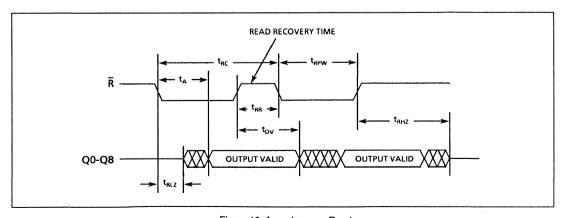

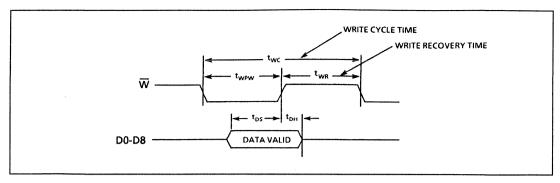

| MA7001                 | 512 x 9-BIT FIFO                                            | 559  |

| MA3764                 | 8192 x 8-BIT MASK-PROGRAMMABLE ROM                          | 574  |

| Type No.         | Databus                                      | Page |

|------------------|----------------------------------------------|------|

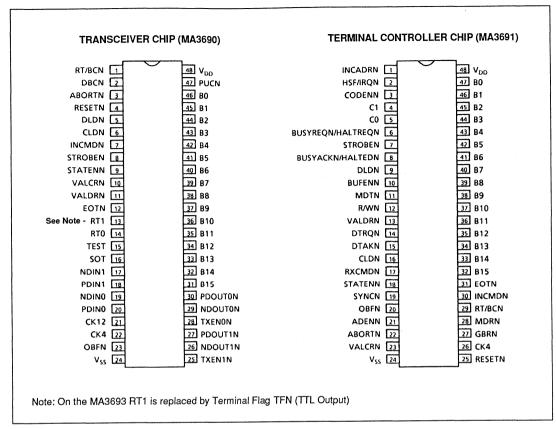

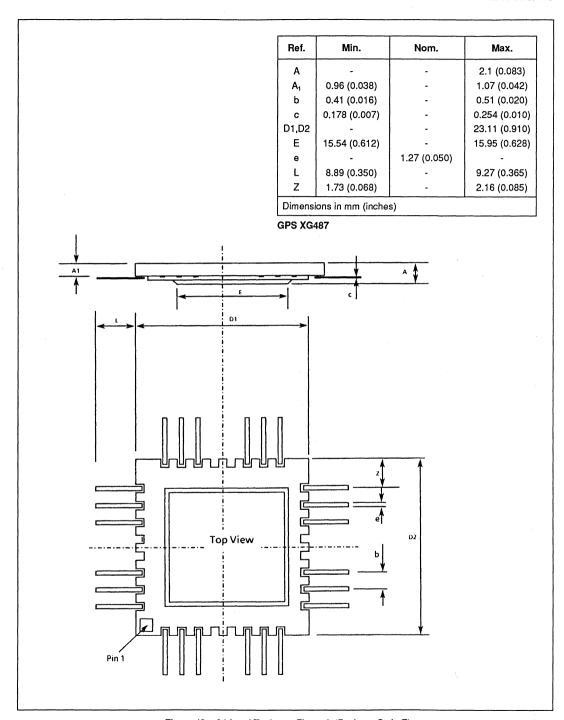

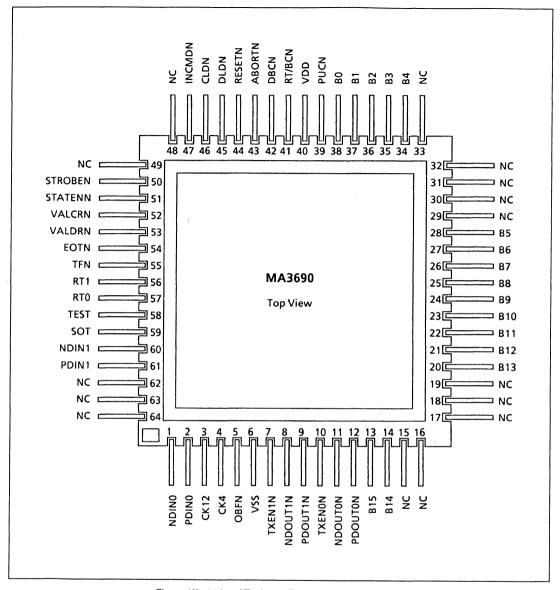

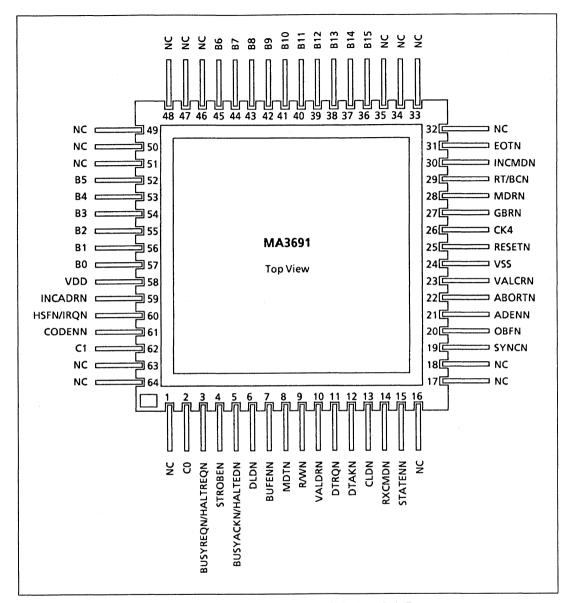

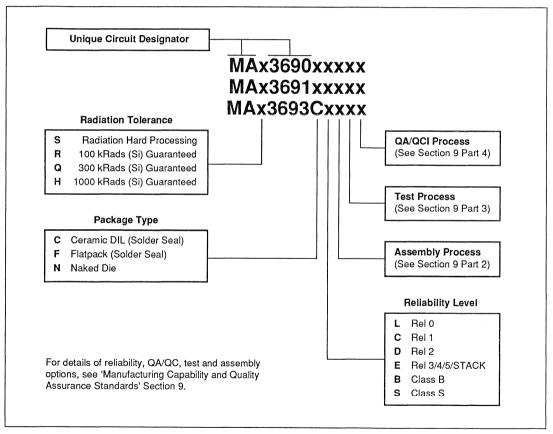

| MA3690/1/3       | 1553B BUS CONTROLLER/REMOTE TERMINAL         | 585  |

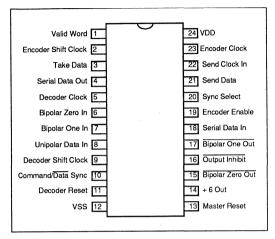

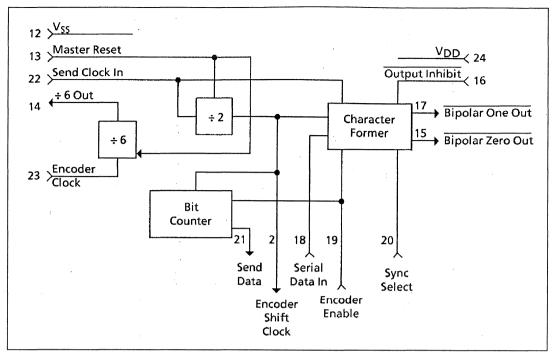

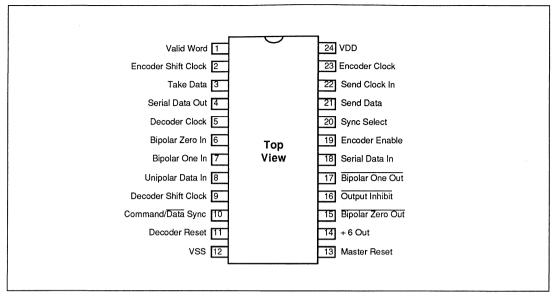

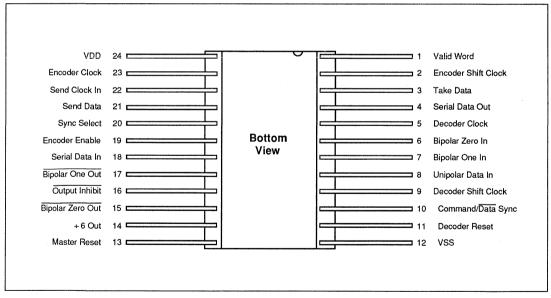

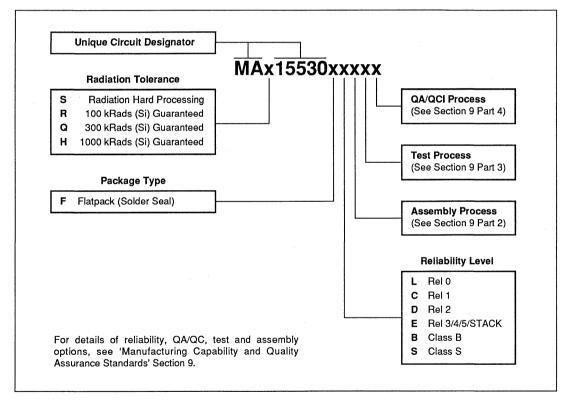

| MAS15530         | MANCHESTER ENCODER/DECODER                   | 625  |

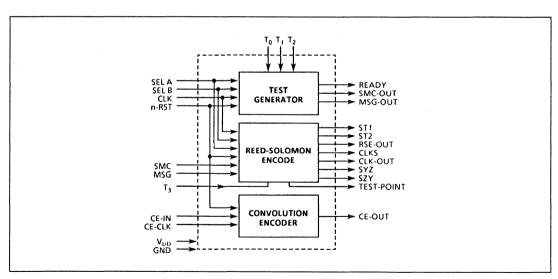

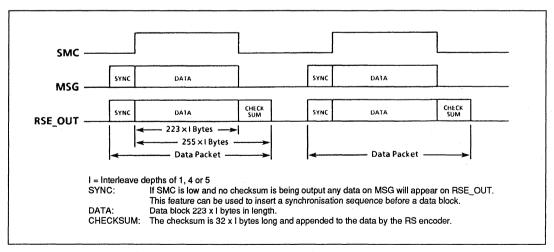

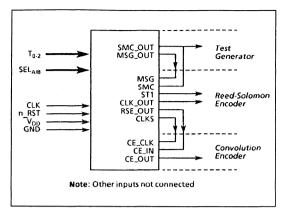

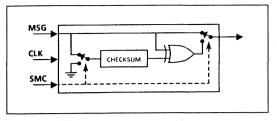

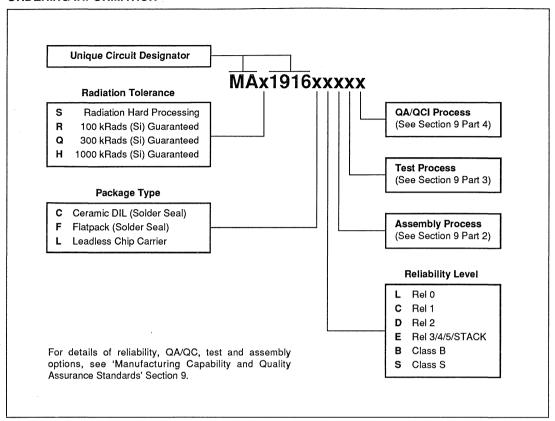

| MA1916           | REED-SOLOMON & CONVOLUTION ENCODER           | 640  |

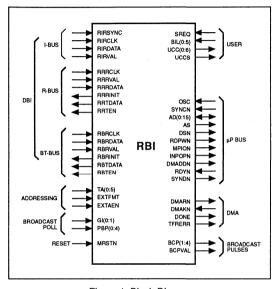

| MA28138          | OBDH REMOTE BUS INTERFACE                    | 651  |

| MA28139          | OBDH BUS TERMINAL                            | 684  |

| MA28140          | PACKET TELECOMMAND DECODER                   | 718  |

|                  | Logic                                        |      |

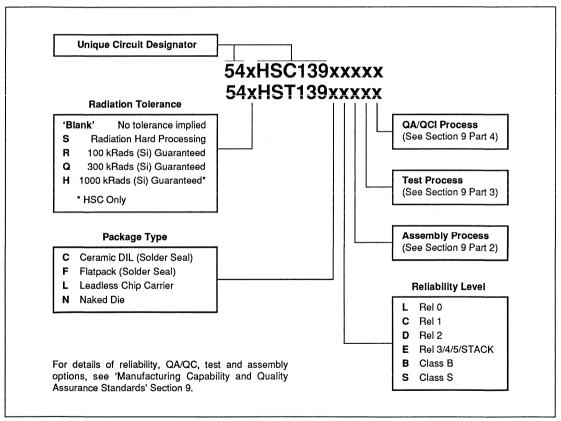

| 15HSC Series     | HIGH SPEED CMOS/SOS LOGIC                    | 791  |

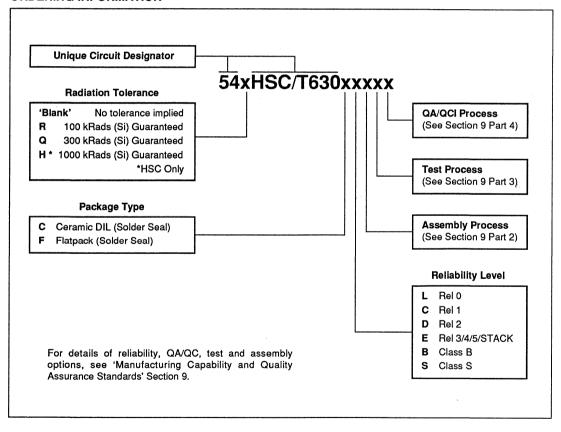

| 54HSC/T Series   | HIGH SPEED CMOS/SOS LOGIC                    | 799  |

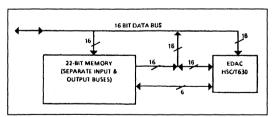

| 54HSC/T630       | 16-BIT PARALLEL ERROR DETECTION & CORRECTION | 899  |

|                  | Semicustom ASICs & Foundry Service           |      |

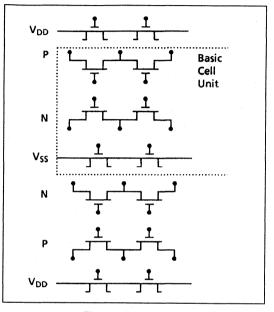

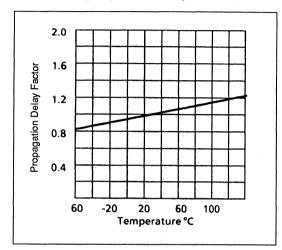

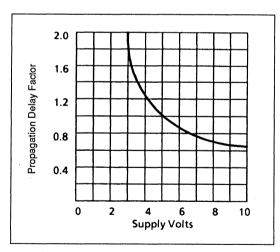

| MA9000A          | ADVANCED GATE ARRAY DESIGN SYSTEM            | 911  |

| MACROSOS 1       | STANDARD CELL DESIGN SYSTEM                  | 917  |

| MA9000 Series    | GATE ARRAYS                                  | 923  |

|                  | ASIC DESIGN ROUTES                           | 930  |

| Bipolar Products | Page                                         |      |

| •                | BIPOLAR PROCESSES & PRODUCTS                 | 935  |

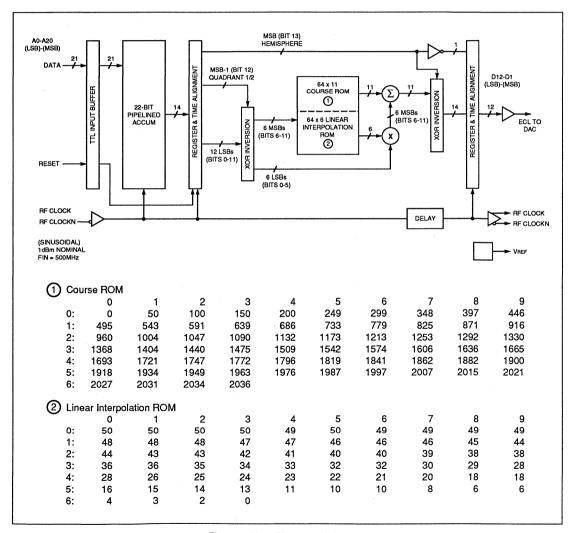

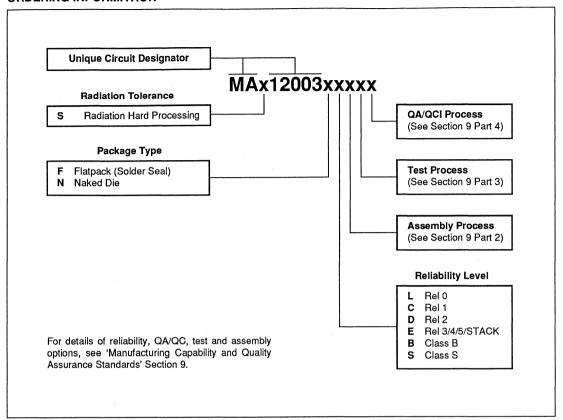

| MA12003          | 22-BIT PHASE ACCUMULATOR/SINE ROM            | 939  |

| WIA 12000        | EL BITTIMOL NOODINGLING. I GINE              |      |

# **GPS Space & Radiation Hard Products Technical Helpline**

Technical and applications assistance with any GPS space product can be obtained from our technical desk direct from the factory on:

Telephone: Int. +44 1522 502274

or +44 1522 502371 (Laboratory) or +44 1522 500500 (Exchange)

Facsimile: Int. +44 1522 502393

or +44 1522 500550

Internet: apps@lincoln.gpsemi.com

Alternatively call your local sales office.

### Hardware & Software Support for MIL-STD-1750 Products

#### Hardware:

Hewlett Packard Offer an HP64000-UX Logic Development System. Essential parts

are the HP64120A, (card cage), the HP64155B (128K memory controller), the HP64302A (trace analyser) and some associated

software. Extra features are available.

Tasco Electronic Services Inc. Offer an MDC281, an HMA31750 and an NMA31750 emulator for

use in conjunction with the HP development system. They allow the user to take full advantage of the emulator capabilities of the HP system and all related design and development aids. Also offered is an HMA31750 Inverse Assembler for use with HP Logic Analyzers.

Tektronix Offer an MAS281 emulator (cannot support 1750B for the

MA31750). Is attached to device in system to offer register access

and step by step debugging facilities.

Tharsys Offer a low cost single-board computer for the NMA31750 with the

BMA31751 (options are available to run the HMA31750 with the

AMA31751).

Software:

TLD Systems ADA cross compiler available for several host machines eg. Digital's

Vax (VMS), Data General Eclipse MV/Family (AOS/VS), HP 9000 series 300 (HP-UX), HP Apollo 9000 series 400 (HP-UX), IBM RISC System/6000 series (AIX) and SUN Microsystem's SPARC and

SUN-3.

Tartan Offer an ADA compiler system to run on a DEC VAX system

(operating system V5.2 or later). Support and debugging tools to be

used in conjunction with the HP or Tektronix emulators are

available.

IPT C cross compiler operating on the VAX (VMS operating system).

GPS Supply on request a 1750 assembler, program downloading

software and a monitor ROM program.

#### **Contact Addresses:**

USA: 5161 Lankershim Blvd Hewlett Packard

No. Hollywood, CA 91601

Tel: (818) 505 5600

Europe: 150, Route du Nant d'Avril

1217 Meyrin 2

Geneva, Switzerland. Tel: (41 22) 780 8111

USA: 1096 East Meadow Circle, **IPT**

> Palto Alto CA 94303

Tel: (415) 494 7500

Tartan USA: Pittsburgh Corporate Office

300 Oxford Drive.

Monroeville PA 15146

Tel: (412) 856 3600

Tasco Electronic Services Inc. USA: 80 Express Street,

> Plainview, NY 11803 Tel: (516) 938 6464

Europe: ADAR Active Technologies B.V.,

Willemsparkweg 100, 1071 HM Amsterdam,

Netherlands Tel: (20) 679 9921

Europe: Alain Dherbecourt Tharsys

Napa Centre, 3, Rue Ariane, Parc Technologie du Canal,

Ramonville 31520

France.

Tel: 61751587

USA: 3625 Del Amo Blvd TLD Systems

Suite 100, Torrance

CA 90503

Tel: (213) 542 5433

#### Introduction

#### The General Electric Company plc

GEC Plessey Semiconductors (GPS) is part of the General Electric Company plc (GEC), which is a wholly British Company. GEC is one of the largest electronics and electrical engineering organisations in the world and, with 160,000 employees is one of the largest UK employers.

GPS offers one of the most extensive ranges of state of the art technologies available in the world. This range includes a variety of CMOS and Bipolar technologies, as well as Power Semiconductor products.

The company has six manufacturing sites worldwide, sales offices in 27 countries and a total of around 3500 employees. There are also 10 design centres strategically placed in different countries to support ASIC design activity and offer technical advice on standard products.

#### **GPS Strategy For Space**

GEC Plessey has a marketing strategy to exploit high growth market areas including communications electronics, ASICs, automotive, computer peripherals and space.

GPS is also one of the few space semiconductor companies operating as a completely independent entity without ties to the OEM equipment market. This means that customers can confidently design with GPS products without concern over security of supply that often accompanies the use of components originating from subsidiaries of competing spacecraft vendors.

GPS now possesses one of the most extensive product ranges in the world specifically targeted at the space market. This product range spans CMOS Silicon On Sapphire (SOS) technology at 0.6 micron, high speed (24GHz) trench isolated bipolar at 0.6 micron gate lengths and a variety of hybrid and microwave circuit capabilities.

GPS will continue the development of new technologies and products with the goal of becoming a first choice supplier for space grade radiation hard components.

# GPS Quality - European Space Agency Capability Approval

The company has a long history of quality approvals. The latest and most notable is the ESA Capability Approval for 2.5 micron SOS products. This Capability Approval was awarded in March 1993. Since that time GPS have been offering both ASICs and standard components with full SCC9000 level B qualification. The ESA Capability Approval for 1.5 micron SOS is ongoing.

To add to the ESA Capability Approval are Self Certifications to MIL-STD-883 for both SOS and bipolar processes. The company now has a number of SMD's lodged with DESC.

#### **CMOS-SOS Integrated Circuits**

The Lincoln based Integrated Circuit operation produces specialist circuits for the space market. The operation employs over 600 people with a very high percentage of graduate level engineering staff.

This IC facility manufactures product for direct sale to end customers and also to other parts of the organisation, where further integration results in more complex products.

The IC facility carries out all manufacturing from design to product shipment in Lincoln, England.

#### **GPS Radiation Hard Silicon on Sapphire**

There is an increasing demand for space and defence systems which can survive radiation effects and ensure continued operation. As satellites and space probes mature, microprocessors, static RAMS, gate arrays and other VLSI ICs with the ability to carry out complex data processing tasks in the extremely stringent environment of space

become essential. Space imposes its own set of requirements, demanding a hardness to radiation which is normally screened out by the atmosphere. This radiation, in the form of cosmic rays, electrons, protons and x-rays, alters the electrical characteristics of circuits and causes a degradation in integrated circuit performance, which can lead to catastrophic device and system failures.

Of all the current silicon-based semiconductor technologies, only CMOS SOS (silicon-on-sapphire) offers the necessary resistance to the hazards of single event upset, transient and total dose radiation. It also provides the advantages of low power consumption and fast internal switching speeds, making CMOS SOS the key technology for defence and space applications. Independent investigators consider that its SEU immunity makes it the only choice for many key space applications

#### **History in CMOS SOS**

The company has been involved in SOS research and development for more than 15 years and is committed to the long term support of SOS processes and products for space and defence applications. Process and design techniques are in unison to maximise the benefits of the technology.

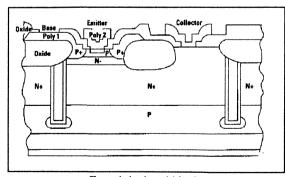

Initial research and development on SOS began at the GEC Hirst Research Centre in 1973. This work continued through to pilot designs which were released in 1979/1980. With the formation of Marconi Electronic Devices in 1981, manufacturing was transferred to the Lincoln facility and a 5 micron process attained full production status in 1982. Development work progressed to achieve smaller geometries and increased radiation hardness. A 3 micron process was established in 1984 and a double level metal variant of this process went into production in 1986. A 2.5 micron variant was introduced in 1989. Both 1.5 and 1.1 micron process is now being used to manufacture memories and semicustom products.

Production processes are based on in-house developed silicon on sapphire technology with drawn gate lengths of 3, 2.5, 1.5 and 1.1 micron. Both

single and double level metal technologies are now available. At the time of publication GPS are in the process of introducing a 0.6 micron Low Power Process in Silicon on Sapphire.

A range of standard products and semicustom capabilities have been developed to provide all the key elements required in space and defence systems.

# SOS Radiation Hardness Summary (1.5 micron)

| Total Dose 1 Digital                | >10 <sup>6</sup> Rad(Si)        |

|-------------------------------------|---------------------------------|

| Dose Rate Survive                   | >1011 Rad(Si)/S                 |

| Dose Rate Upset                     | >1012 Rad(Si)/Si                |

| Single Event Upset (Errors/Bit day) | <4 x 10 <sup>-11</sup> Neutrons |

| Latch Up                            | Not Possible                    |

#### SOS Performance Summary (1.5 micron)

| Transistor Count | >400K           |

|------------------|-----------------|

| Toggle Frequency | >100MHz         |

| Gate Delay       | <1.0ns          |

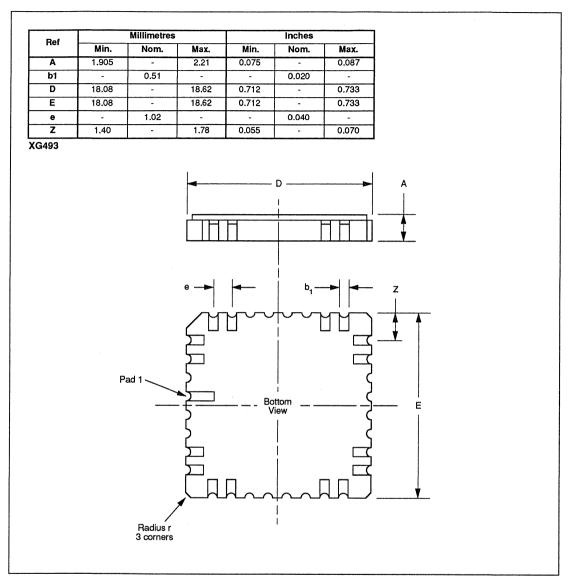

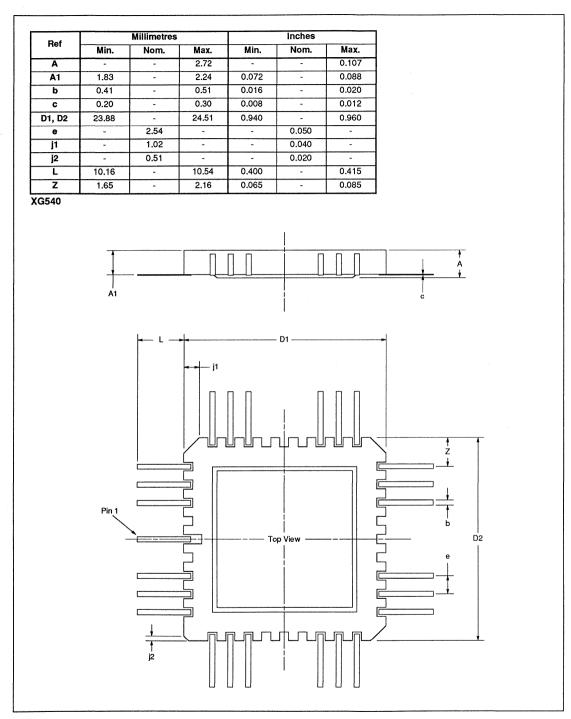

| Pin Count        | 172             |

| Power            | <1.0μW/MHz/Gate |

#### Wafer Fabrication

The Lincoln wafer fabrication facility was established in 1981 and has been substantially extended and enhanced to its current capacity of 2500 wafer starts per week. A range of CMOSSOS processes are run in the facility covering feature sizes from 5 to 0.6µm. Wafer size is 4 in.

All manufacturing groups operate on a 24 hour per day, 3 shift basis producing ASICs, memory circuits and microprocessors up to space standards. All manufacturing processes are controlled by means of a computer-aided manufacturing system (PROMIS) which extends through wafer fab, assembly, and test. Extensive use is made of this system to collect wafer related engineering data which is then processed using statistical software packages.

#### **Facilities**

Integrated manufacturing facilities consist of 17,000 sq. ft of wafer fabrication clean room (with separate areas for manufacturing and development), 9000 sq. ft of assembly floor (part Class 100 clean room), a 6000 sq. ft test floor and 2000 sq. ft of characterisation area. Additional laboratory space is provided for functions such as product engineering.

The wafer fabrication area is primarily built to Class 100 standards with 200 sq. ft of Class 10 area which is utilised for, the critical steps in the 1.5μm SOS process and development programs on 0.6μm technology. These areas are environmentally controlled to temperature control limits of +0.5°C and humidity control of +2.5%. Particulate counts indicate an environment which is close to Class 1. Utilities installations are to an appropriate standard with all process gases run in continuously welded stainless steel lines using purifiers and point of use filtration as appropriate. A high purity de-ionising water ring main is provided for sub 1.0μm geometry processes.

Continuous monitoring of many facility parameters is carried out by a computer based building management system and this provides the ability to datalog and generate trend data for these parameters Where appropriate these measurements are backed up by manual measurement such as bacteria counts, carried out on a regular basis in the DI water system.

#### Computer Aided Manufacture

The PROMIS computer aided manufacturing system is used to define all process flows and to track material through development and mainstream manufacturing.

By this method it is possible to cope with a wide variety of process flows with minimal risk of human error and also to provide a high degree of visibility of batch status to anyone within the 400 strong user group. A natural consequence of the use of PROMIS is total traceability of material from incoming material to finished devices.

#### **Product Assembly**

The assembly capability is contained within the Lincoln (UK) facility except for plastic encapsulation (offshore) and tin plating (Power Division, Lincoln). The preseal assembly facility is enclosed in cleanroom conditions. Space products have been isolated in their own module to provide additional focus on these high quality components. The area offers total facilities for military and space manufacture of integrated circuits on one site. Current product being produced to these levels of quality include static RAMS, MIL-STD-1750 processors, standard logic circuits, MIL-STD-1553 databus products, and ASICs.

The present capacity of this assembly area is 10,000 units per week. Expansion over the next 12 months will increase the space capacity. The area also offers an engineering quick turnaround route for development prototypes and engineering experiments.

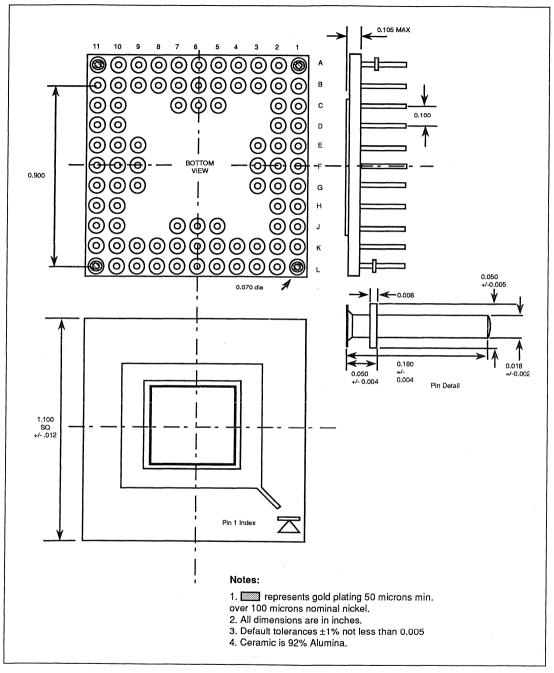

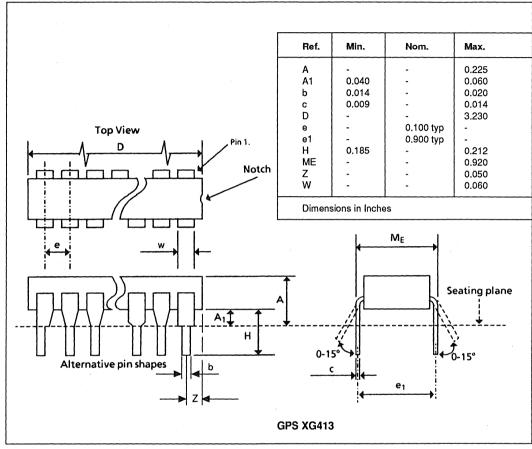

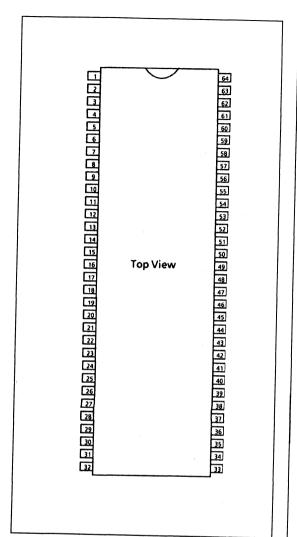

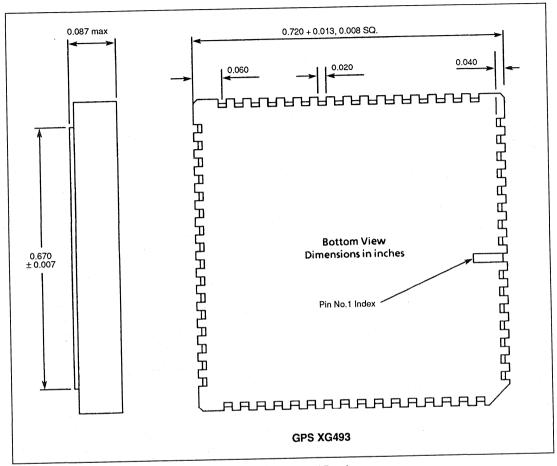

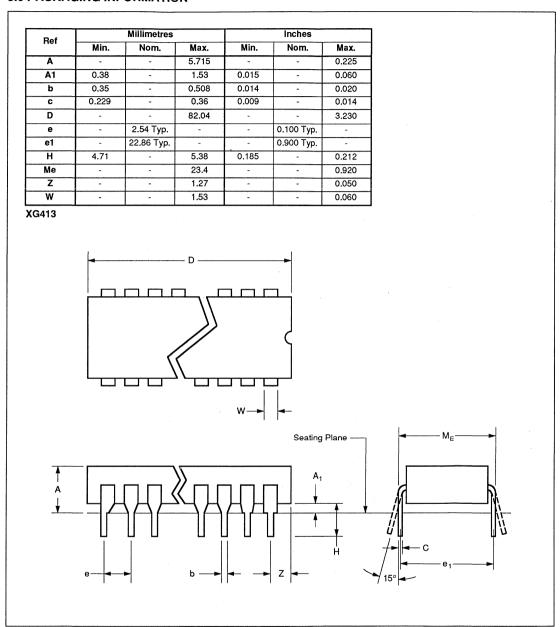

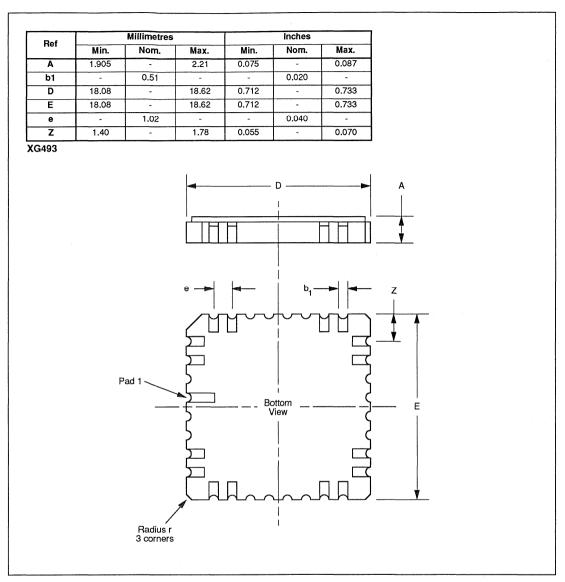

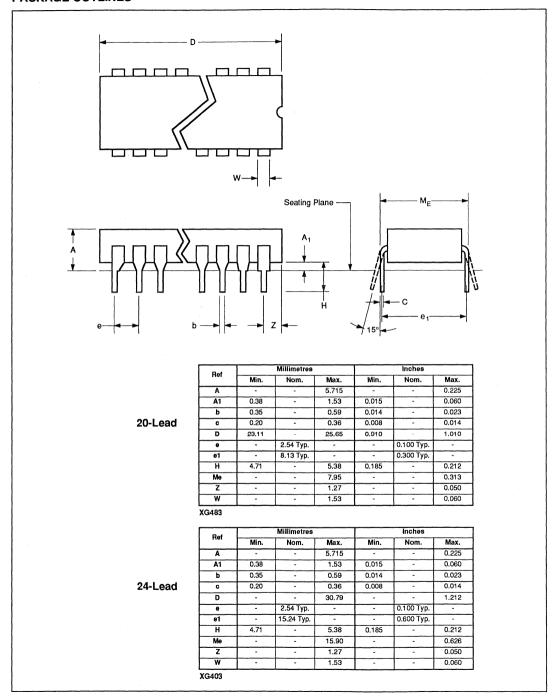

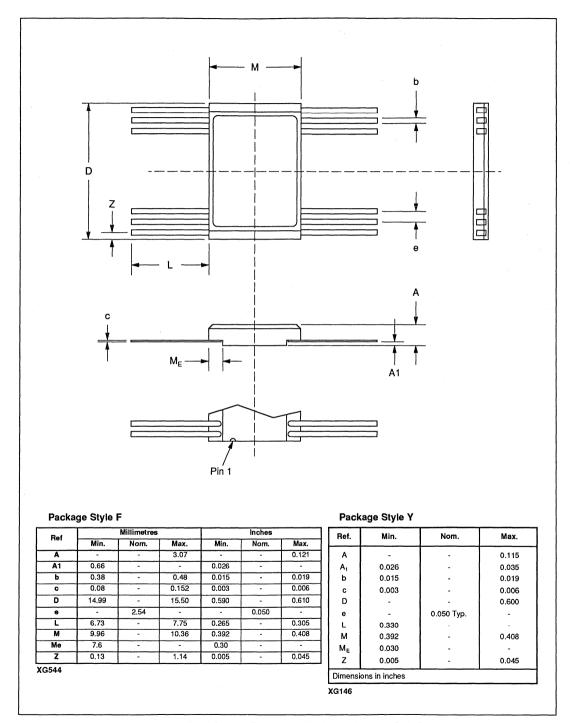

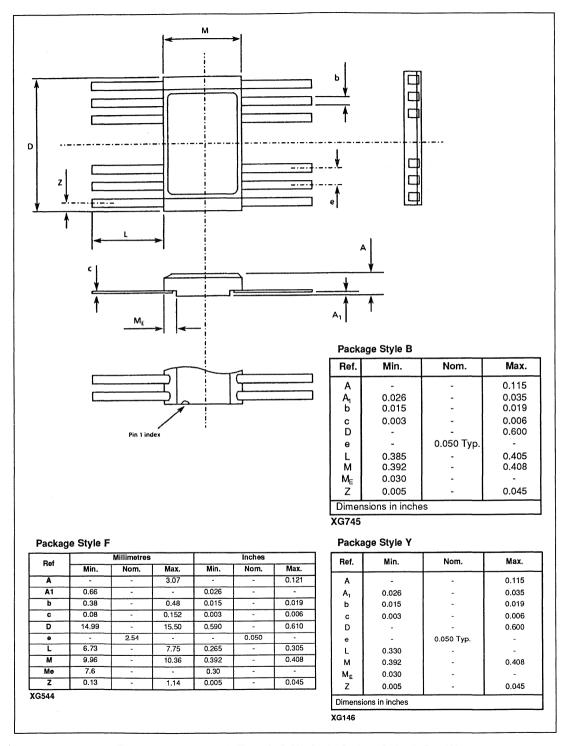

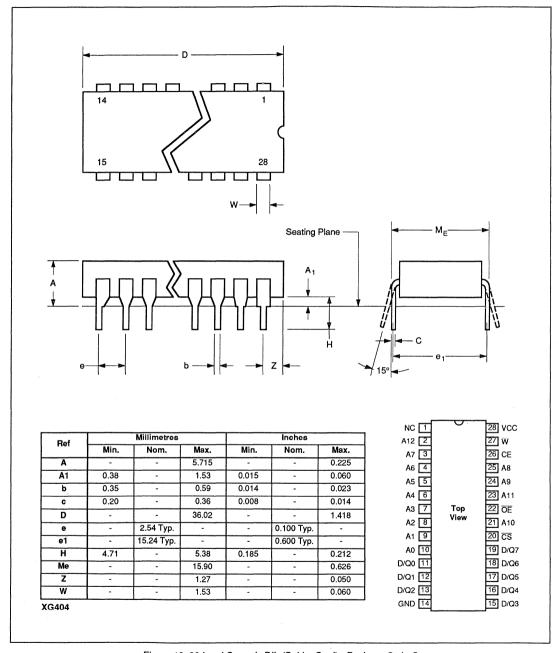

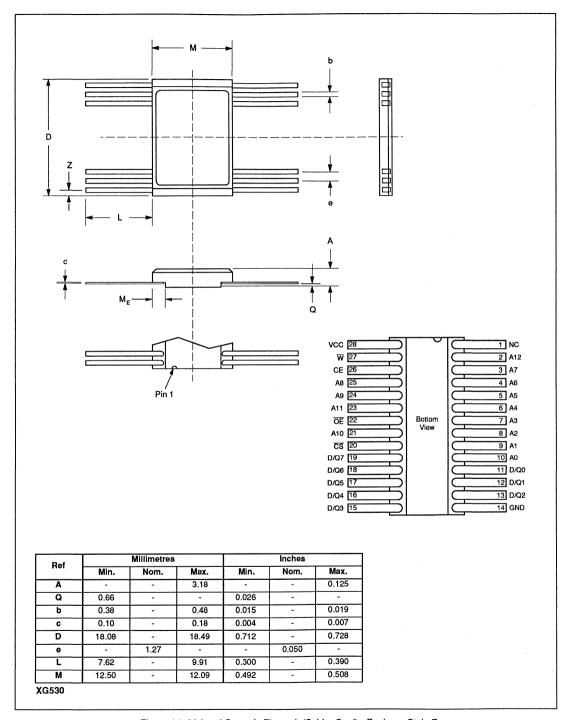

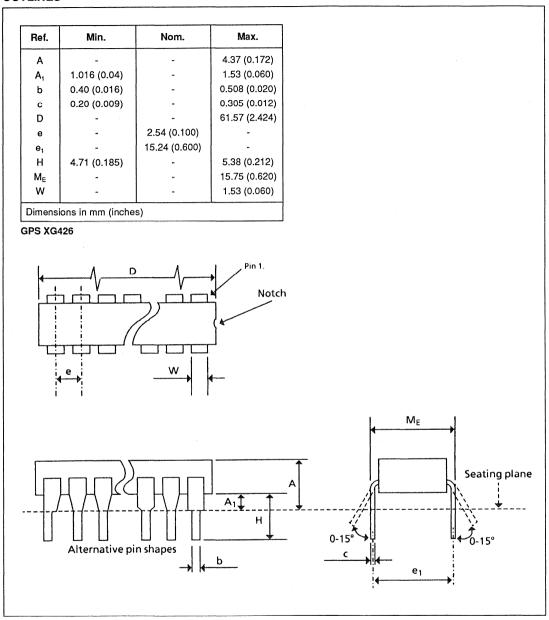

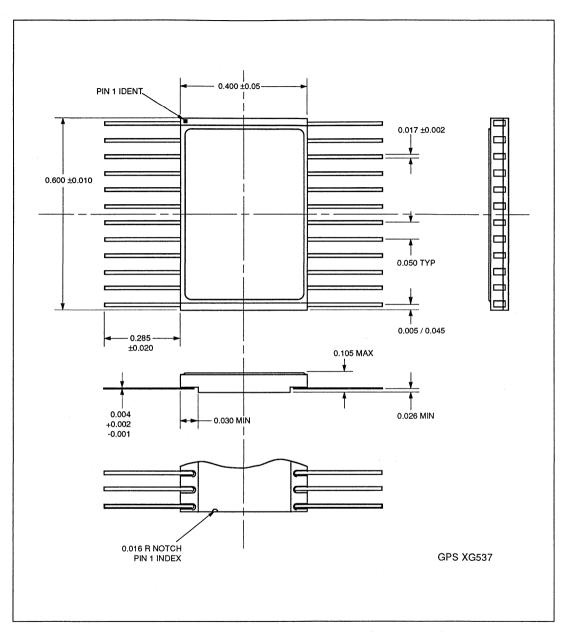

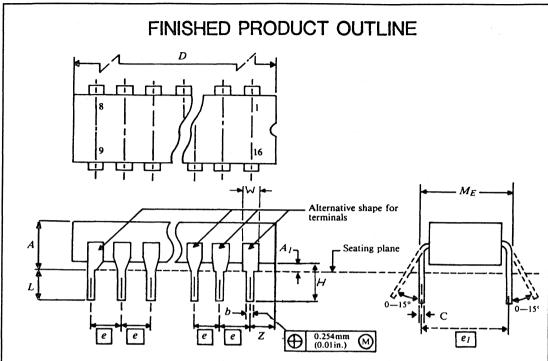

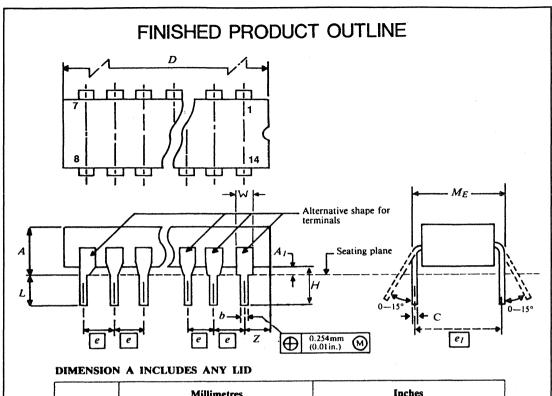

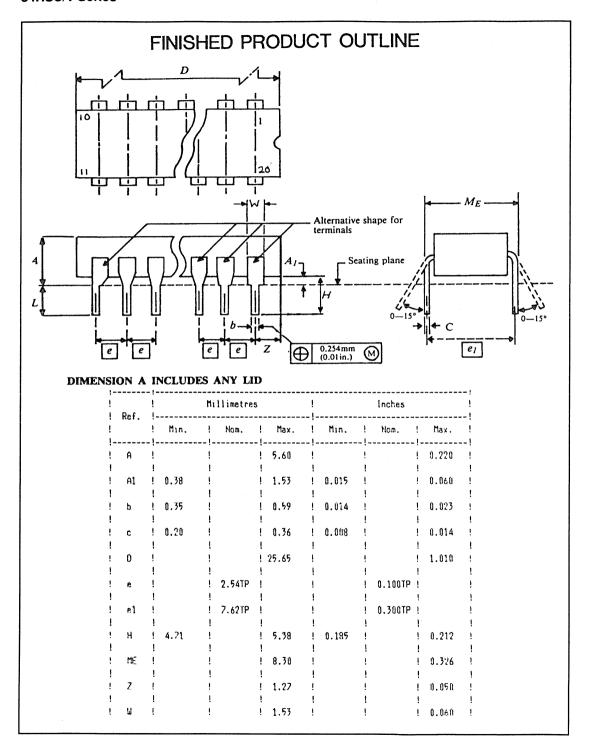

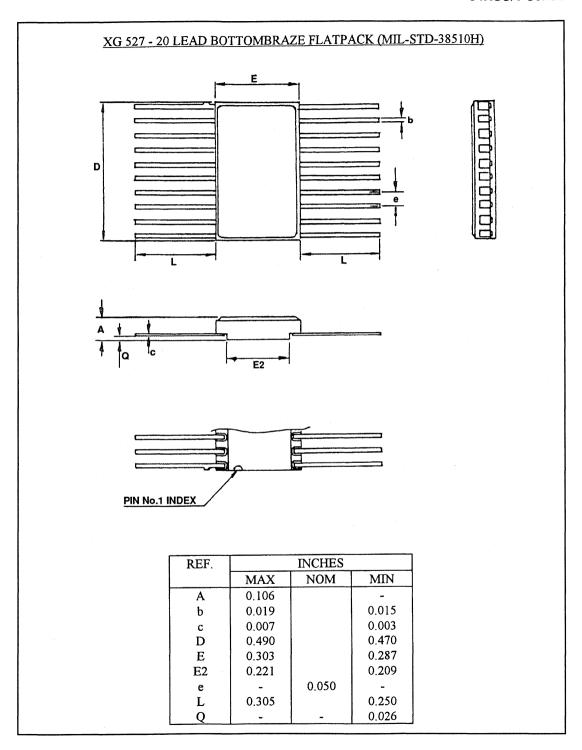

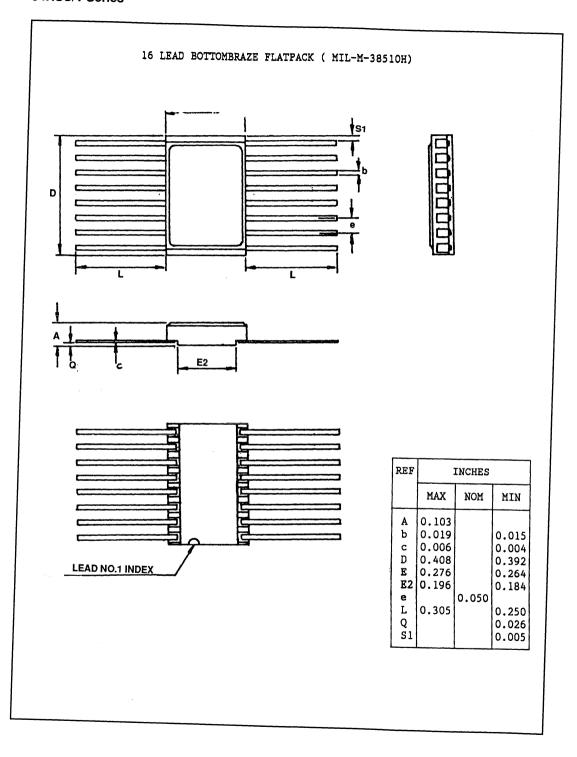

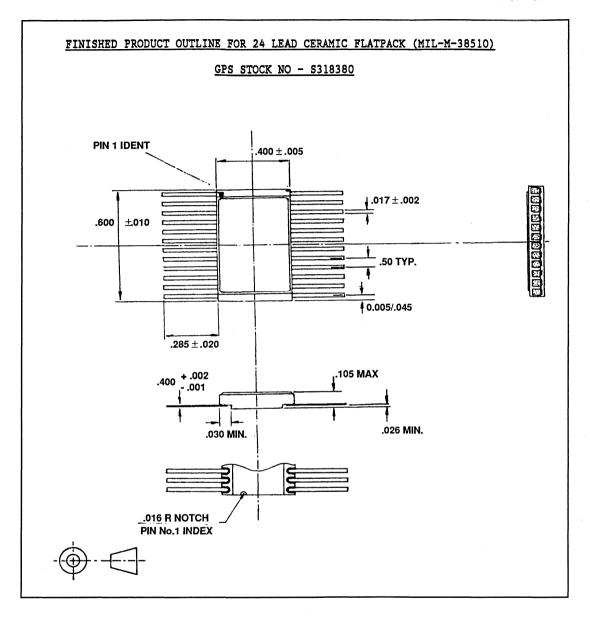

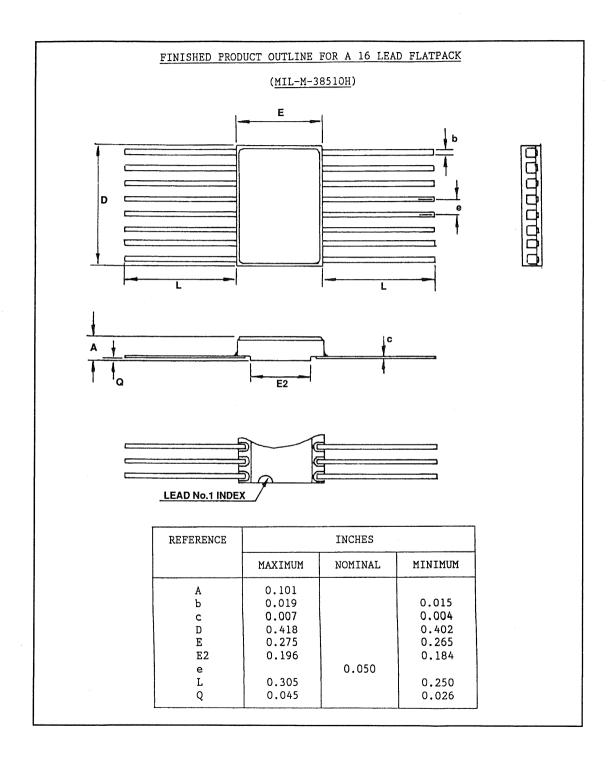

The assembly area has facilities for the production of bulk silicon CMOS and silicon on sapphire devices in numerous package styles, including custom designed packages for special applications. Current capability includes:

Dual in line - Sidebrazed and Cerdip, Leaded Flatpack, Cerpac, Leadless Chip Carrier, Pin Grid Arrays, Cerquads (J Lead and Gullwing), and Small Outline Packages (SO). Sealing methods include solder seal with Kovar or ceramic lids, glass seal and conformal coatings.

A surface mounting facility has been established to mount Class S leadless chip carriers onto motherboards to produce 1750 processor and RAM modules.

The company offers a manufacturing flow capable of screening to MIL-STD-883C class S and B, European Space Agency and British Standard quality levels.

#### **Basic Structures Characterisation**

DC measurements can be performed on a range of test systems all with pA current and mV voltage resolution.

A KEITHLEY 250 is utilised for routine wafer assessment, where large quantities of data can be stored and analysed using the KEITHLEY database analysis routines. For more detailed manipulation/analysis, data can be easily transferred to the VAX system where GPS developed routines are available.

More rigorous and detailed testing can be achieved using a HP4145 parametric analyser controlled by a HP310 computer. Connection via a 40-channel relay matrix to an autoprober enables any specific parameter to be measured across the whole area of a wafer.

Software has been developed for instrument control as well as for data manipulation and analysis to produce colour histogram/wafermap outputs. Data can be transferred from the HP computer to the VAX, using terminal emulator software, where analysis using existing statistical software programs can be performed Radiation effects can be studied using another HP4145/matrix/computer configuration linked to an ARACOR x-radiation system.

The 10-keV x-rays are produced within a leadlined cabinet, which also contains an autoprober and dosimeter. Connecting wires are passed through a shielded orifice which enables devices to be biased or measured during irradiation. Software can be developed to repeat a cycle of test, bias, and irradiate for assessment of total dose effects, without the need to open the cabinet. Facilities are available to test devices either in package or wafer form Dose rates are determined by a suitable choice of tube current and voltage, within the range 0 25 to 160 Krads (Si02)/min.

Measurements of capacitance parameters use a HP4192 impedance analyzer, which has a resolution down to 10fF and a frequency range of 5Hz to 13MHz. A built-in power supply enables a bias of up to +35V to be applied to the device under test. A conductance value can also be obtained within

the range 1 ns to 10 S. It has a four terminal configuration making precise measurements possible when using a correctly designed test-box. Wafer measurements utilise two coaxial probes situated on a manual prober within a screened light-proof cabinet, keeping strays and external EM interference to a minimum. This equipment can be controlled by a computer where specific software can easily be written to set up, trigger and return results from the instrument.

#### **Test Capability**

The test area consists of some six digital testers with capabilities up to 100MHz and 256 pins. A Fairchild 5588 Memory Tester is used to test memory devices up to speeds of 25MHz.

This ATE is supported by a wide range of automatic probers and environmental handlers, coupled with temperature sources, enabling full military and space level testing to be carried out Control of the calibration of equipment, test programs, test hardware, test methodology, practices, and device flow is maintained by an extensive quality control system, ensuring compliance to the various commercial, military, and space quality screening levels. Procedures for handling static sensitive device within the area

The computer-aided manufacturing (CAM) system, using PROMIS software, is installed in this area to control work progress, provide traceability and return results from analysis.

#### **Burn-in/Life Test**

Extensive burn-in facilities offer screening at any temperature up to 150°C Burn-in voltages can be provided up to +15 volts for particular devices. The ovens have continuous monitoring of both temperature and voltage to ensure complete reliability Sequential switching of device supplies and controlled cooling is incorporated into the device flow wherever necessary. Both static and dynamic burn-in is carried out in this area to MIL-STD-883C, ESA 9000, BS9000, and commercial standards.

High volume standard products have dedicated burn-in modules, but reconfigurable modules are available for rapid response, covering a wide range of standard packages, DIP, PGA, LCC, Cerquads, etc.

Burn-in times may vary from 1 hour to 500 hours for production screening, 100 to 200 hours for QCI testing and 2000 to 6000 hours for specific qualification exercises. Specific areas are used for engineering investigations and specialised exercises demanding modified equipment/monitoring.

#### The SOS Product Range

A range of products and capabilities has been developed to ensure that all the major elements in a radiation hard system are available and fully supported. The product strategy is to continue to develop products to increase the performance of the following families and release them to the appropriate military and space quality levels.

#### Microprocessors

The key microprocessor product is the high performance (2 MIPs) 1750 microprocessor. Designated as the MA31750, it meets the requirements for higher speed processing of both 1750A and 1750B instruction sets in space and military applications.

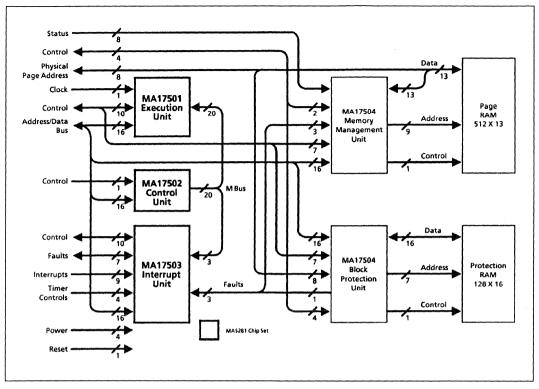

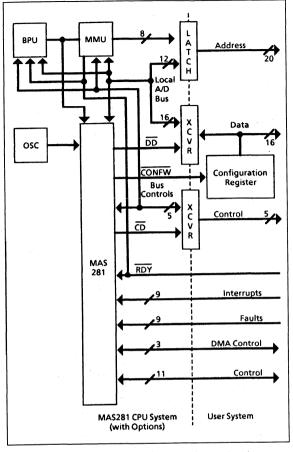

Also in the processor range is the MAS281 MIL-STD-1750A microprocessor. Based on the McDonnell Douglas MDC281, the GPS version has been enhanced to make it what was for a number of years the only viable radiation hard, space grade, 1750A microprocessor. It is supported by a range of standard peripheral devices to satisfy standard system functions.

#### Memories

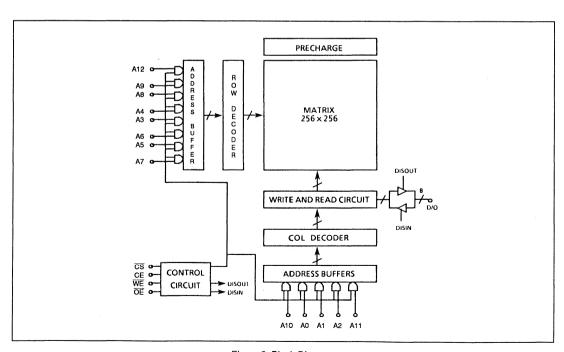

A range of static random access memories (RAM) has been developed specifically for radiation hard applications. As the products have evolved from 1K bits to 64K bits, process and design techniques have been refined resulting in progressively harder and faster components.

Read Only Memory (ROM) is offered as a capability with either base or metal programming ROM is also used in standard products such as microcode ROM and databus protocol look-up tables.

Simple logic functions and octal transceivers, latches, buffers, decoders and multipliers have been included in the SOS product range to allow non-standard functions to be configured which do not justify a semicustom development. Innovative techniques allow new products to be rapidly introduced and a wide range of devices to be manufactured with minimal lead time and cost penalties.

#### Databus

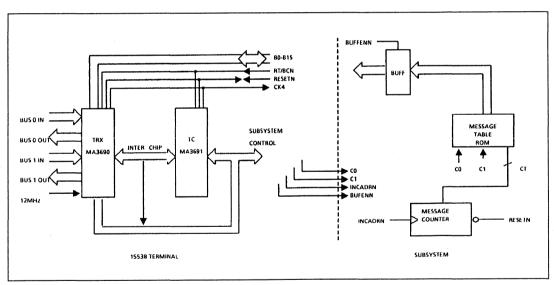

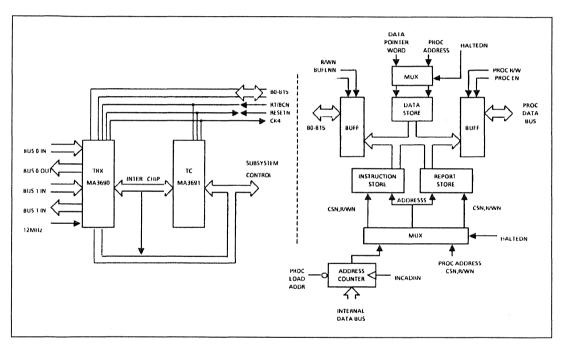

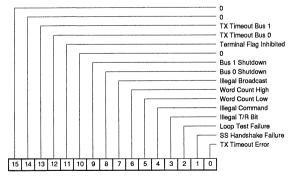

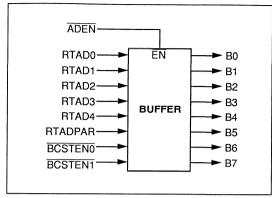

GPS has been a leading supplier of MIL-STD-1553 products for more than a decade. In 1982, the first full protocol LSI chip set was demonstrated. A more powerful, radiation hard chip set has now been produced.

The MIL-STD-1553B protocol was originally defined for military avionic systems but is now used in other military systems and is being designed into future space projects.

#### Semicustom

Gate arrays ranging in complexity from 700 to 60,000 gates provide rapid access to the SOS technology for non standard functions. For more complex designs, an extensive standard cell library enables design engineers to quickly and consistently produce radiation hard circuits to meet customers' specific requirements.

#### Mixed Analogue and Digital

Standard products and standard cells have been produced for such functions as analogue to digital, and digital to analogue converters, comparators and operational amplifiers.

#### **Radiation Performance**

An integrated circuit is said to be radiation hard if it can continue to function within its specifications after exposure to a stated amount of radiation. On Earth, the atmosphere shields systems at ground level from most gamma and x-rays, electrons and heavy ions which occur in space, can change the electrical properties of integrated circuits and adversely affect system performance. Defence applications are also demanding increasing tolerance to a variety of radiation effects. Although all semiconductors have some intrinsic resistance to radiation, CMOS SOS is the only technology which is tolerant to all radiation effects.

#### **Accumulated Total Dose**

The total dose hardness of an integrated circuit is a measure of its ability to withstand accumulated doses of high energy radiation in the form of gamma or x-rays. In the space environment, the ionising radiation that is absorbed by a device is accumulated over a long period of time; typically 100KRad (Si) over a 10 year operating life, but may be significantly higher depending on mission.

lonizing radiation causes electron-hole pair generation in the oxide Recombination occurs immediately, but under a positive bias electrons are swept to the gate electrode within pico seconds. The less mobile holes move towards and eventually are trapped in the silicon silicon dioxide interface region, causing a negative threshold voltage shift. The effect of these changes to the core elements of the circuit range from input threshold degradation to functional failure and high static supply leakage.

Total dose hardness up to the 1M Rad(Si) level is only achieved by a constrained design system and special attention to critical process steps ,especially gate oxide growth. Detailed knowledge and analysis of radiation effects using the in-house gamma and x-ray facilities is also required.

#### Transient Dose

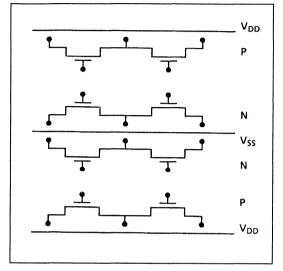

One well known problem with most technologies is their vulnerability to high transient doses of ionising radiation. These pulses have been shown to induce the latch up. CMOS circuits have certain parasitic transistors associated with adjacent P and N channel devices .These parasitics are configured so as to approximate a silicon controlled rectifier (SCR). The photo-current induced in these structures by a severs burst of ionising radiation can be sufficient to turn on the SCR. This then initiates a large, self perpetuating current flow capable of causing great damage to the device Once latched, a circuit can only be returned to correct operation (if not permanently damaged), by a power down/power up procedure.

It is physically impossible for a SOS device to suffer from latch up. In SOS, each transistor is made on an individual silicon island. These islands are isolated from each other by removing all epitaxial silicon from non-active areas, leaving only insulating sapphire substrate. This removes the possibility of any parasitic structures existing between transistors, and thus completely prevents latch up.

The other effect of transient radiation is to cause data corruption in stored cell elements. This corruption is caused by the inability of the power rail to hold up the voltage on a node sufficiently to maintain the data (power rail collapse). The voltage drop is as a result of the transient burst generating a photocurrent, the magnitude of which is proportional to total junction area. The CMOS SOS technology gains its high tolerance to transient radiation from the fact that much smaller photocurrents flow and hence voltage drop along

the supply is lower. This is due to the fact that the junction area is confined to only the thin epitaxial layer rather than the much larger junction and well depletion volumes which occur on conventional CMOS processes.

Evaluations have shown corruption levels of up to 1x10<sup>12</sup> Rad(Si) Sec-1 and will survive without permanent degradation levels of >1x10<sup>13</sup> Rad(Si) Sec-1 on RAMS fabricated on the 1.5 micron SOS process.

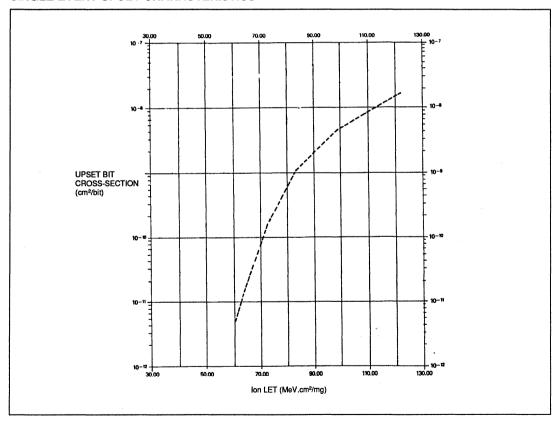

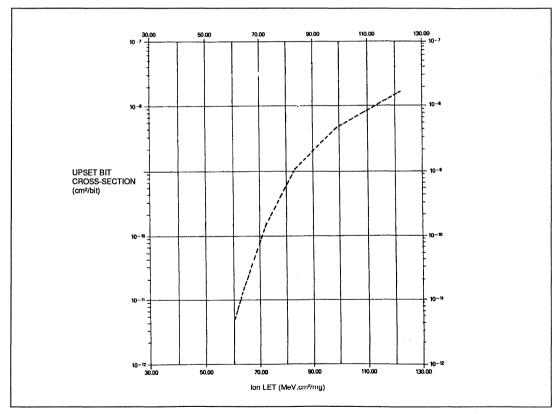

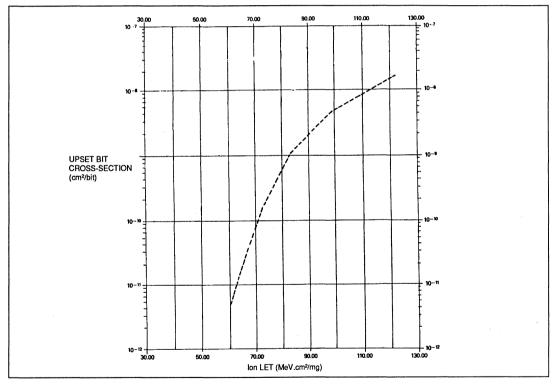

#### Single Event Upset

SEU within a memory cell can be defined as the corruption of data caused by the creation of a charge in a circuit by a heavy particle ion. There is no permanent or long term damage to the circuit, data becoming valid again after the next write operation.

As a charged particle passes through a semiconductor, it will lose energy by ionisation. If a charged particle passes through a reverse-biased p-n junction, the electron-hole pairs generated in the device depletion region will be separated by the high electric field. The high carrier density created along the particle's track will distort the electric field of the junction depletion region. The field will be spread along the particle track and create a field funnel. The charges in this funnel will be collected by drift and will add to the charge collected in the junction depletion region.

If sufficient charge is deposited on the parasitic gate and junction capacitance, a voltage transient will appear. The voltage transient created by an event on a node can then cause the logic state of the cell to be inverted. The charge required to invert the state of the memory cell is referred to as the critical charge

Silicon on Sapphire technology offers significant advantages in this area. The physical structures of SOS transistors with their individual, totally isolated silicon islands, lead to much smaller 'junction depletion region' volumes than bulk CMOS technologies.

The charged particle can also induce latch up in bulk CMOS circuits. For the reasons outlined in the previous section this is not possible on CMOS SOS.

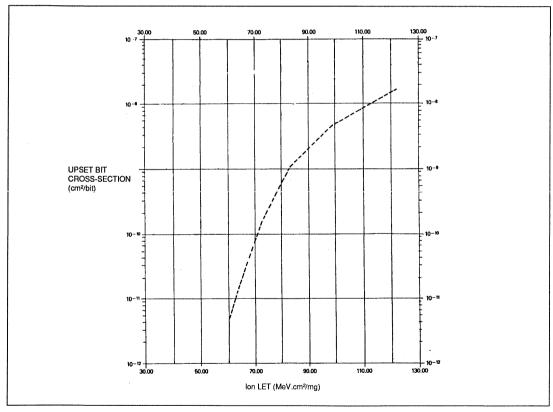

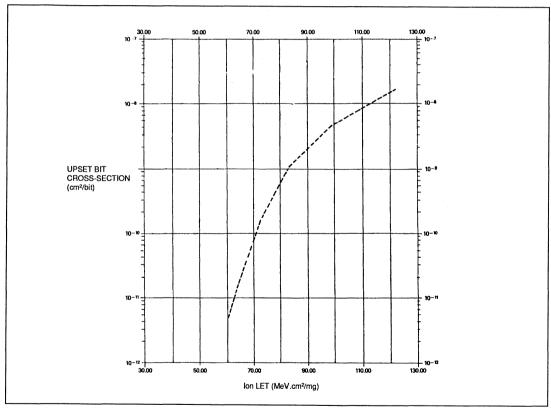

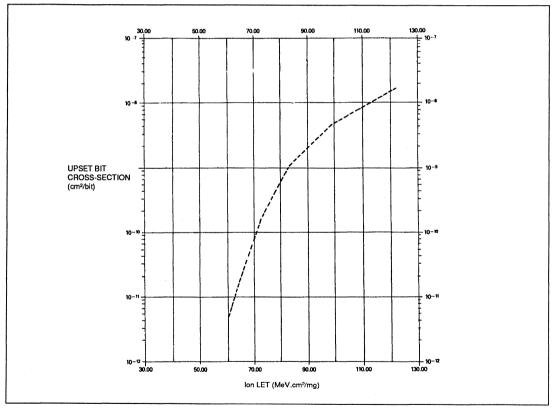

Evaluations carried out on a Cyclotron by the European Space Agency have shown a threshold LET of 59.4 Mev/(mg/sq. cm) for a 64K memory. The MA31750 has been evaluated on a Van de Graaff facility and found to just start upsetting at the 170 Mev/(mg/sq. cm) level. Both these devices are fabricated on the 1.5 micron process.

#### Neutron Radiation

CMOS SOS is inherently hard to neutron radiation. The main effect of neutrons are to degrade the silicon lattice giving rise to recombination sites. This has the effect of reducing minority carriers lifetime which has a significant effect on bipolar technologies.

CMOS SOS in common with all MOS is a majority carrier technology and is therefore largely unaffected. SOS Devices have been proven to with stand neutron radiation to greater than 10<sup>15</sup> neutrons/cm<sup>2</sup> (the limit of the equipment used) without significant degradation of critical device parameters.

# Section 1 Microprocessors

# MA31750

#### HIGH PERFORMANCE MIL-STD-1750 MICROPROCESSOR

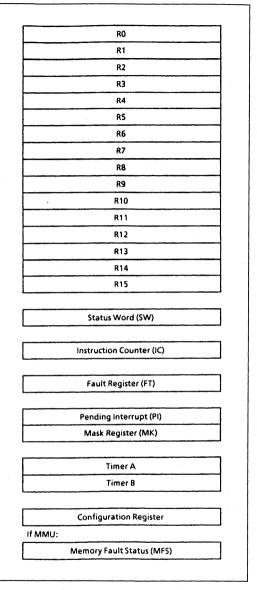

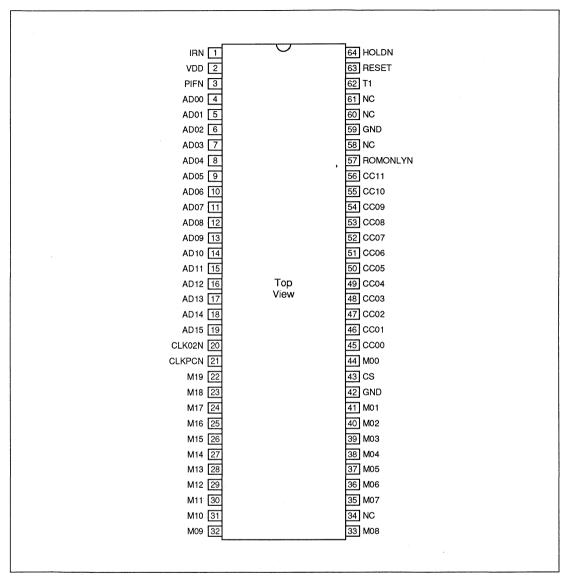

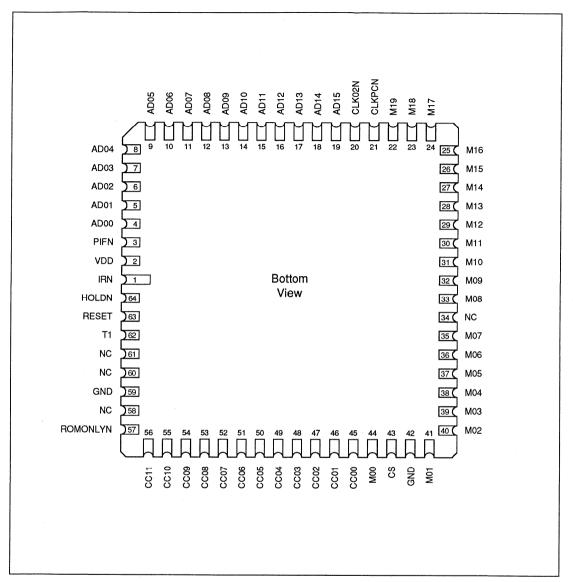

The GEC Plessey MA31750 is a single-chip microprocessor that implements the full MIL-STD-1750A instruction set architecture, or Option 2 of Draft MIL-STD-1750B. The processor executes all mandatory instructions and many optional features are also included. Interrupts, fault handling, memory expansion, Console, timers A and B, and their related optional instructions are also supported in full accordance with MIL-STD-1750.

The MA31750 offers a considerable performance increase over the existing MAS281. This is achieved by using a 32-bit internal bus structure with a 24 x 24 bit multiplier and 32-bit ALU. Other performance-enhancing features include a 32-bit shift network, a multi-port register file and a dedicated address calculation unit.

The MA31750 has on-chip parity generation and checking to enhance system integrity. A comprehensive built-in self-test has also been incorporated, allowing processor functionality to be verified at any time.

Console operation is supported through a parallel interface using command/data registers in I/O space. Several discrete output signals are produced to minimise external logic.

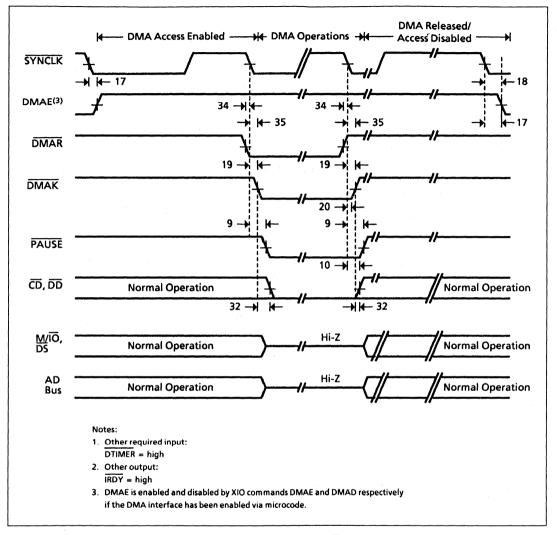

Control signals are also provided to allow inclusion of the MA31750 into a multiprocessor or DMA system.

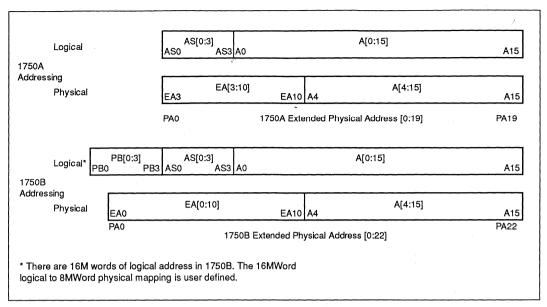

The processor can directly access 64KWords of memory in full accordance with MIL-STD-1750A. This increases to 1MWord when used with the optional MA31751 memory management unit (MMU). 1750B mode allows the system to be expanded to 8MWord with the MMU.

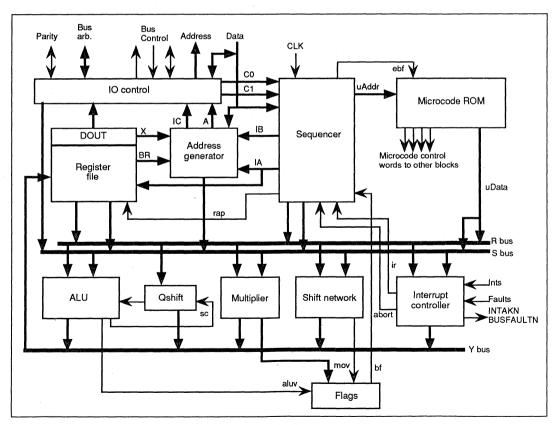

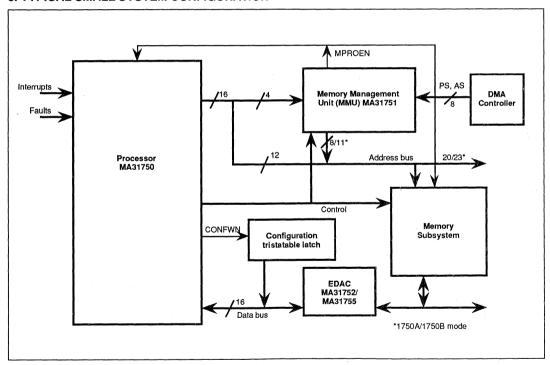

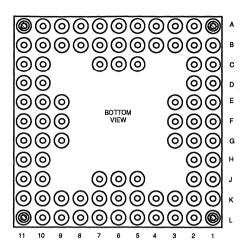

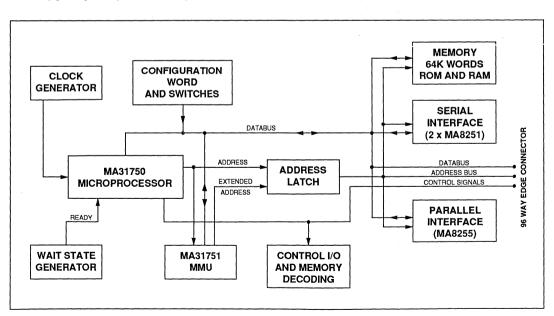

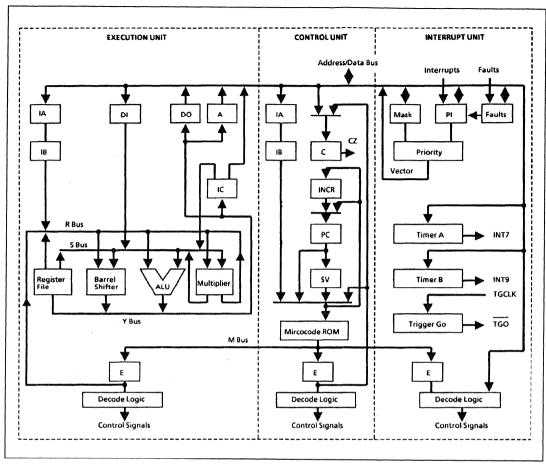

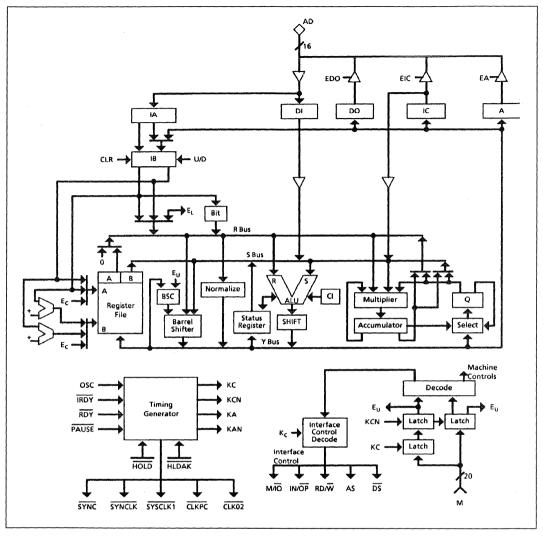

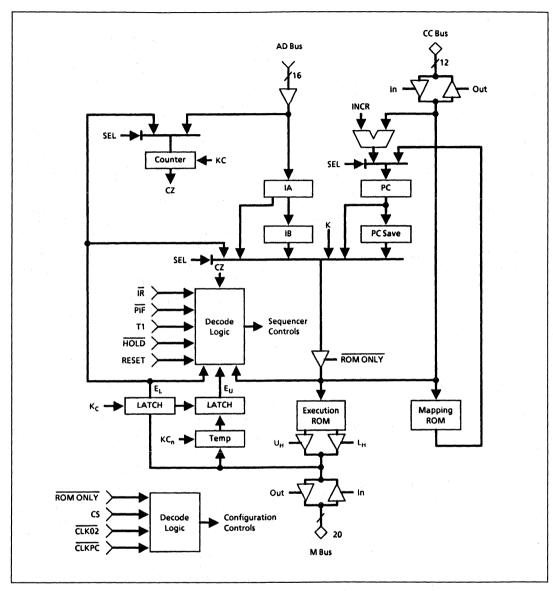

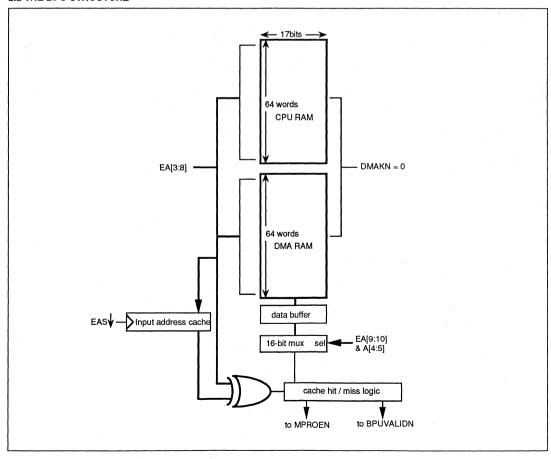

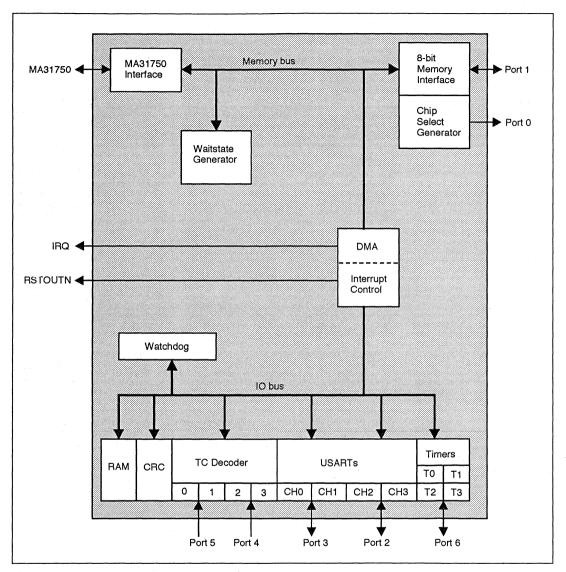

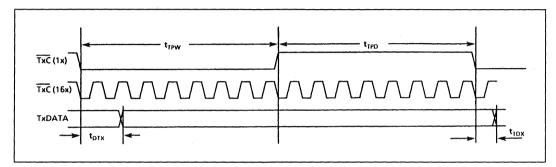

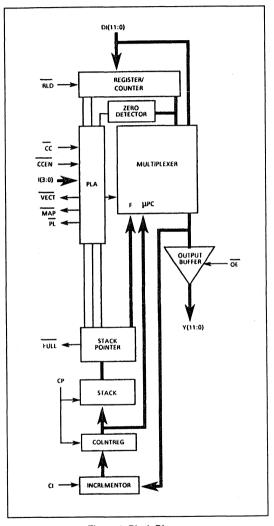

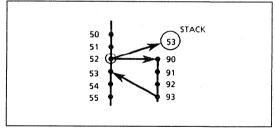

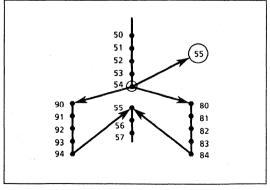

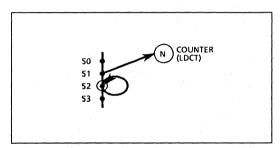

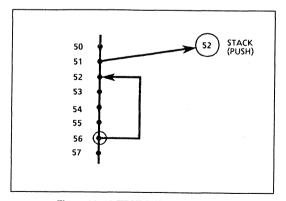

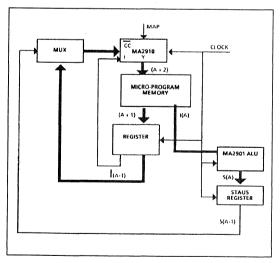

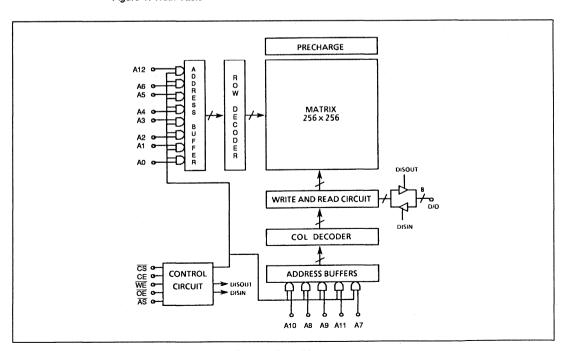

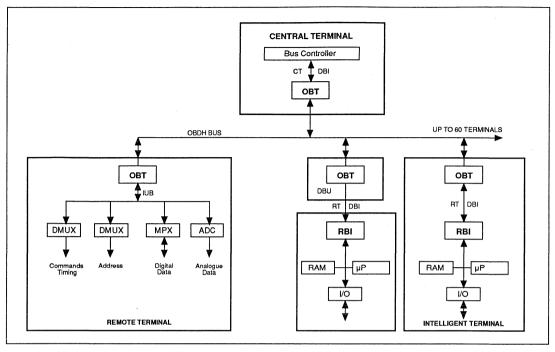

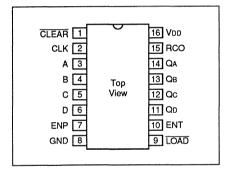

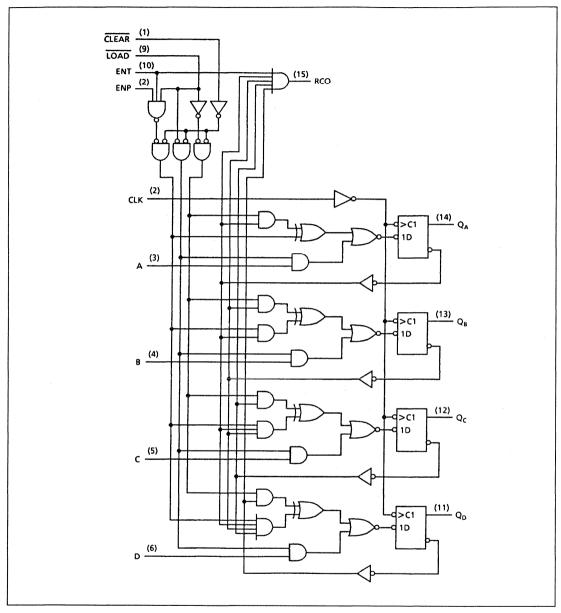

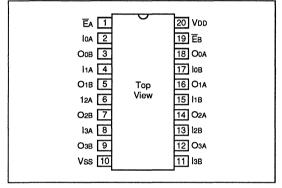

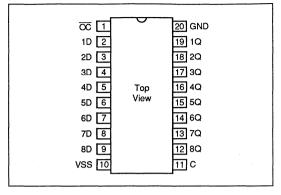

Figure 1: Architecture

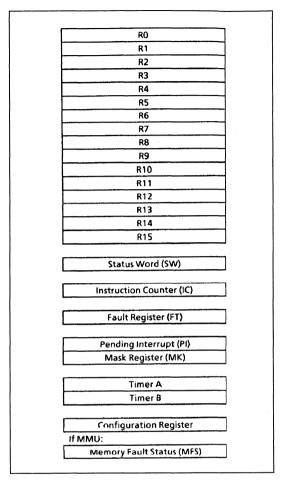

#### 1. ARCHITECTURE

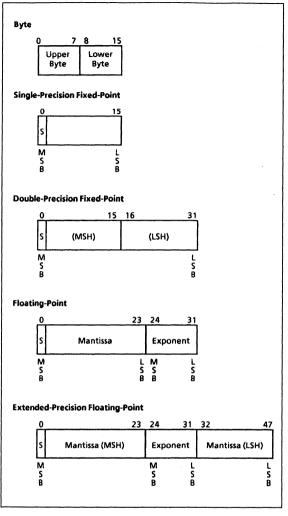

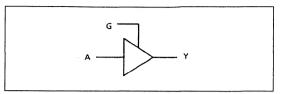

The GEC Plessey MA31750 Microprocessor is a high performance implementation of the MIL-STD-1750A (Notice 1) Instruction Set Architecture. Figure 1 depicts the architectural details of the chip. Two key features of this architecture which contribute to the overall high performance of the MA31750 are a 32-bit shift network and a 24-bit parallel multiplier. These sub-systems allow the MA31750 to perform multi-bit shifts, multiplications, divisions and normalisations in a fraction of the clock cycles required on machines not having such resources. This is especially true of floating-point operations, in which the MA31750 excels. Such operations constitute a large proportion of the Digital Avionics Instruction Set (DAIS) mix and generally a high percentage of many signal processing algorithms, therefore having a significant impact on system performance.

Key features include:

- A three-bus (R, S, and Y) datapath consisting of an arithmetic/logic unit (ALU), three-port register file, shift network, parallel multiplier and flags block;

- 2) Four instruction fetch registers C0,C1, IA, and IB;

- 3) Two operand transfer registers DI, and DO;

- 4) Two address registers IC and A;

- 5) A state sequencer;

- 6) Micro-instruction decode logic.

The relationship between these functional blocks is shown in Figure 1.

#### 2. ADDITIONAL FEATURES

The MA31750 may be operated in one of two basic user selectable modes. 1750A mode follows the requirements of MIL-STD-1750A (Notice 1) and implements all of the mandatory features of this standard. In addition, many of the optional features such as interval timers A and B, a watchdog timer and parity checking are included. 1750B mode, when selected, allows the user access to a range of new instructions and features as described in the Draft MIL-STD-1750B, Option 2. These include a range of unsigned arithmetic operations and expanded addressing support instructions.

#### 2.1. MIL-STD-1750 OPTIONAL FEATURES

In addition to implementing all of the required features of MIL-STD-1750A and the Draft standard MIL-STD-1750B, the MA31750 also incorporates a number of optional features. Interval timers A and B as well as a trigger-go counter are provided. Most specified XIO commands are decoded directly on the chip and an additional set of commands, associated with MMU and BPU operations, are also decoded on chip.

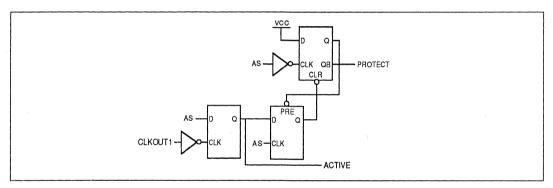

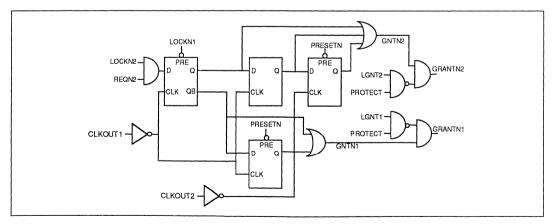

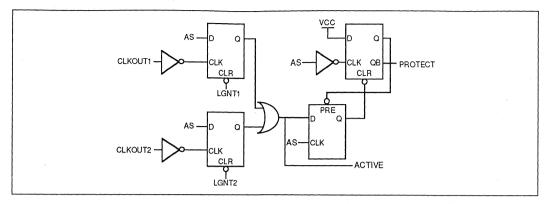

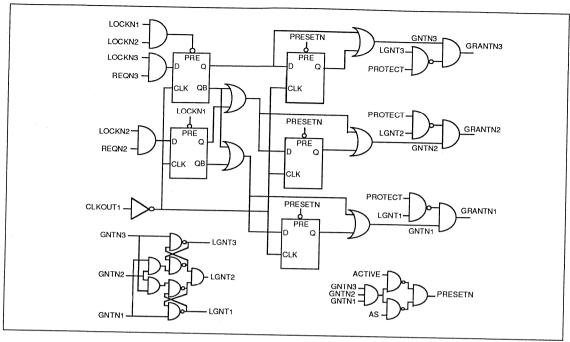

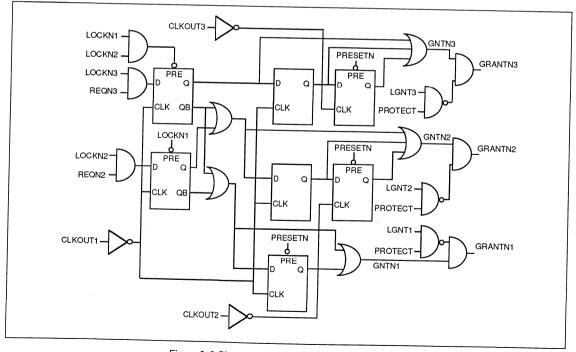

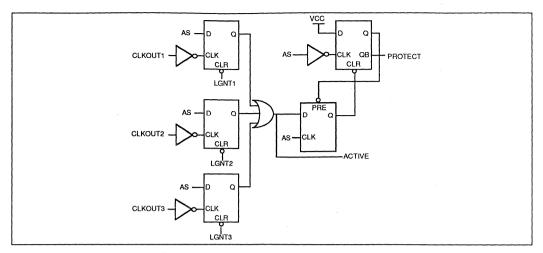

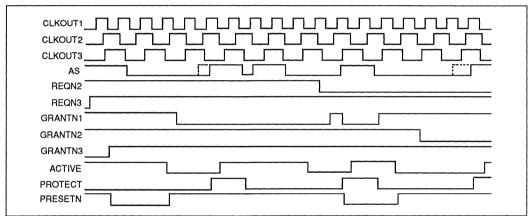

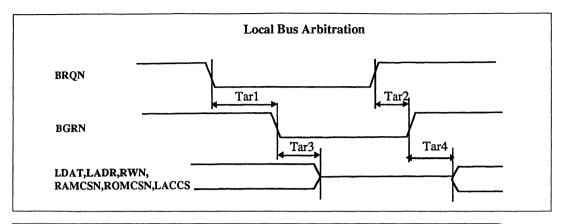

#### 2.2. BUS ARBITRATION

The MA31750 has a number of extra control lines to allow its use in a system utilising multiple processors. A bus request and grant system coupled with external arbitration logic allows common data and address buses to be used between devices. A lock request pin is also provided to allow the processor to maintain control of the buses when modifying areas of shared memory.

#### 2.3. MEMORY BLOCK PROTECTION

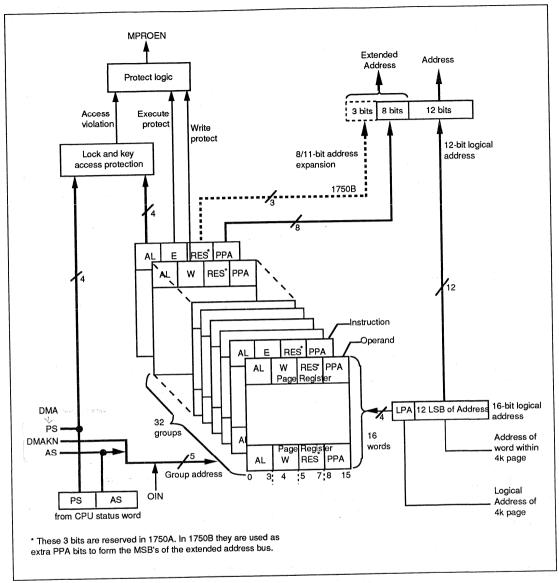

The basic MMU function allows write or execute protection to be applied on 4KWord block boundaries. This may be further resolved to 1kWord blocks by the inclusion of a Block Protect Unit (BPU). The MA31751 can act as both an MMU and a BPU in 1750A mode, operating with the full compliment of 1MWord of memory. It will also support expansion to 8MWord in accordance with Draft MIL-STD-1750B.

#### 3. MODES OF OPERATION

MA31750 operating modes include: (1) initialisation, (2) instruction execution, (3) interrupt servicing, (4) fault servicing, (5) timer operations and (6) console operation.

#### 3.1. INITIALISATION

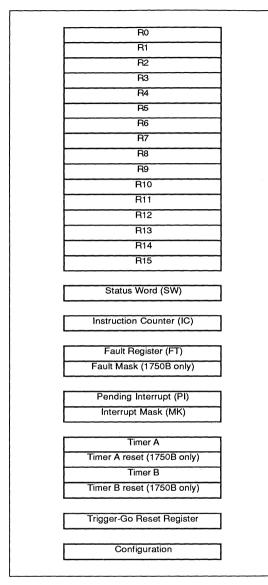

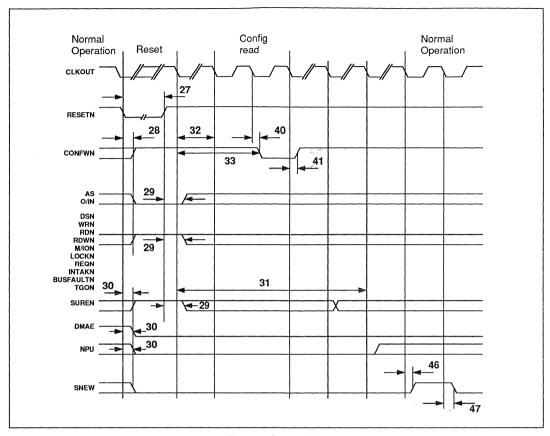

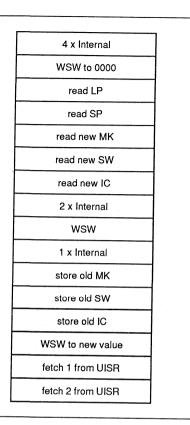

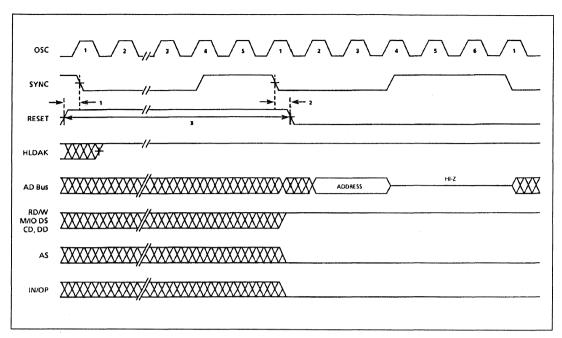

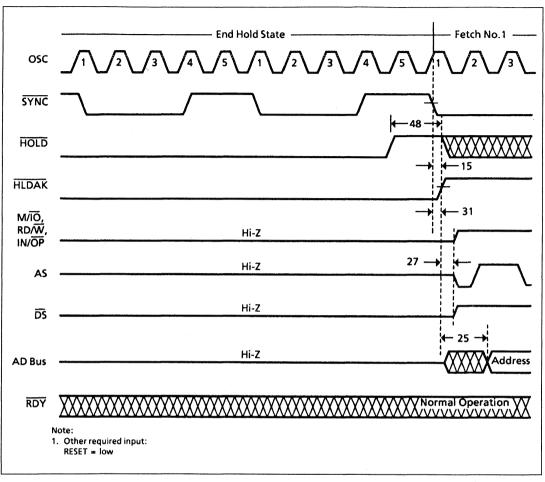

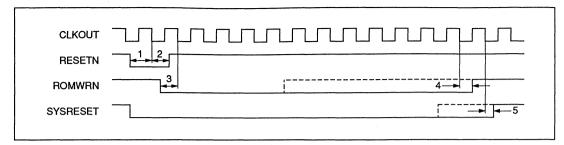

The MA31750 executes a microcoded initialisation routine in response to a hardware reset or power-up. Figure 3 shows a cycle-by-cycle breakdown of this routine. The operations performed are dependent on the system configuration read by the processor during startup. Figure 2 summarises the resulting initialisation state.

| MA31750                       |                     |  |

|-------------------------------|---------------------|--|

| Instruction Counter           | Zero                |  |

| Status Word                   | Zero                |  |

| Fault Register Zero           | Zero                |  |

| Fault Mask Register (1750B)   | All ones            |  |

| Pending Interrupt Register    | Zero                |  |

| Interrupt Mask Register       | Zero                |  |

| General Registers             | Undefined           |  |

| Interrupts                    | Disabled            |  |

| Timers A and B                | Zeroed and started  |  |

| Timer Reset Registers (1750B) | Zero                |  |

| Trigger-Go Counter            | Reset and started   |  |

| TGON Line                     | High                |  |

| Start-Up ROM                  | Enabled             |  |

| DMA                           | Disabled            |  |

|                               |                     |  |

| MMU                           | · ·                 |  |

| Page Registers AL/W/E fields  | Zero                |  |

| Page Register PPA field       | Logical to physical |  |

|                               |                     |  |

| BPU                           |                     |  |

| Memory Protect RAM            | Zero (disabled)     |  |

| Global Memory Protect         | Enabled             |  |

Figure 2: Initialization State

The last action performed by the initialisation routine is to load the instruction pipeline. Instruction fetches start at memory location zero with AS = 0, PS = 0 and PB = 0 and will be from the Start-Up ROM (SUR) if implemented. Whether BIT passes or not, the processor will begin instruction execution at this point. The system start-up code may include a routine to enable and unmask interrupts in order to detect and respond to a BIT failure if required.

| Addr | Operation                                          |

|------|----------------------------------------------------|

| 0    | PIC initialised                                    |

| 1    | A< 0x8410                                          |

| *2   | Read external configuration register from 8410H    |

|      | (CONFWN asserted low)                              |

| 3    | _                                                  |

| 1F   | -                                                  |

| 20   | If BPU, N< 128 else N< 0                           |

| 21   | Decrement N; branch to 21 if N >= 0                |

| 4    | Write internal configuration register              |

| 5    | -                                                  |

| 6    | If no MMU, br to 7                                 |

| 13   | -                                                  |

| 14   |                                                    |

| 15   | N < 256                                            |

| 16   | Decrement N                                        |

| *17  | Write MMU Instruction Page Register N              |

| *18  | Write MMU Operand Page Register N; branch to 16 if |

|      | N > 0                                              |

| 19   | A < 0400H                                          |

| 1A   | N < 16                                             |

| 1B   | PBSR < N                                           |

| 1C   | <u> </u>                                           |

| *1D  | Write Memory control register to MMU with PB = N   |

| 1E   | Decrement N; branch if N >= 0 to 1B                |

| 7    | A < 0                                              |

| 8    | IC < A                                             |

| 9    | Br to BIT if required                              |

| Α    | -                                                  |

| В    | Br if no SUR to 00D                                |

| С    |                                                    |

| D    | Re-init PIC                                        |

| E    | -                                                  |

| *F   | Zero SW                                            |

| 10   | •                                                  |

| 32   | 1-                                                 |

| 33   | Br to 011 if BIT passed (or not run)               |

| 34   | <u> </u>                                           |

| 35   |                                                    |

| 36   | Set FT bit 13                                      |

| 11   | Init DMAE, SUREN, NPU                              |

| 12   |                                                    |

| *3F8 | Fetch first word from 0                            |

| *3F9 | Fetch second word from 1                           |

|      | First instruction first cycle                      |

<sup>\*</sup> Indicates an external cycle

Figure 3: Initialization Sequence

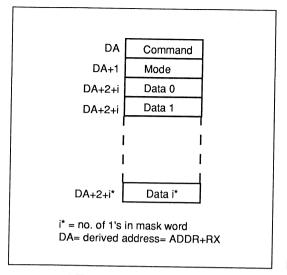

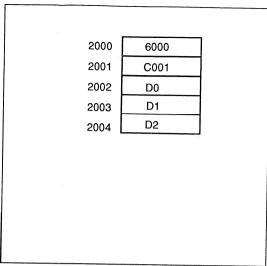

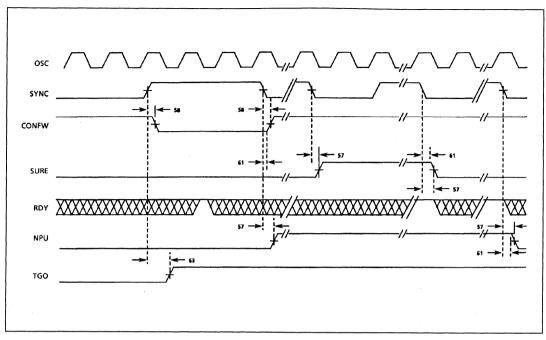

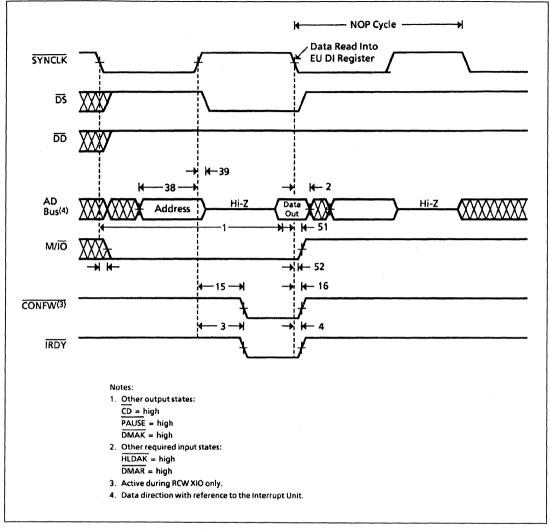

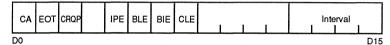

#### 3.1.1. CONFIGURATION REGISTER

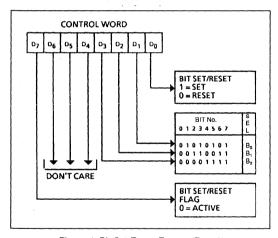

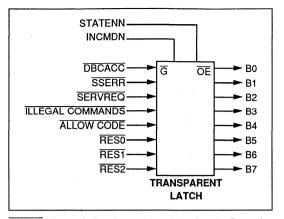

The system configuration register allows the MA31750 to function with a variety of different system designs. Implemented features such as a BPU should be indicated as present by settling bits in an externally-implemented 16-bit latch - see figure 4 for bit assignments. The latch must be placed in IO space at the address defined by XIO RCW (8410) shown in the table of XIO commands, Figure 20c. The processor decodes this command internally and produces a discrete output signal CONFWN which may be used as the external register Output Enable control.

| Bit   | Function                                    |

|-------|---------------------------------------------|

| 0     | MMU Select 0                                |

| 1     | BPU Select 0                                |

| 2     | 1 = Console operation enabled               |

| 3     | MMU Select 1                                |

| 4     | Interrupt sensitivity (1 = level, 0 = edge) |

| 5     | MMU Select 2                                |

| 6     | Parity sense (1 = odd, 0 = even)            |

| 7     | 1= BIT on power-up                          |

| 8     | 1 = Start-Up ROM present                    |

| 9     | 1 = DMA device present                      |

| 10    | 1=1750A mode, 0=1750B mode                  |

| 11    | 1=Instruction set expansion enabled         |

| 12    | BPU Select 1                                |

| 13    | BPU Select 2                                |

| 14-15 | Reserved for future expansion               |

Figure 4: Configuration Word Bits

The processor maintains an internal configuration register which is updated from the external register during initialisation and during the execution of a NOP/BPT (No-op/Breakpoint) instruction. The internal configuration register is used to control the CPU. Note that although the external register can be read using XIO RCW, this does not affect the internal configuration. Note: if the interrupt level/edge trigger select bit - (bit 4) is changed in the internal register during normal operation of the device, one or more spurious interrupts may occur.

When in 1750B mode, the processor needs to know how many Page Banks are implemented in the external system so that Status Word changes can be protected properly. MIL-STD-1750B allows the options 0,1,2,4,8 or 16. The actual selection should be coded into the three configuration register bits MMU0, MMU1 and MMU2 as shown in figure 5.

In 1750A mode, setting any of the MMU select bits indicates the presence of an MMU, the actual code is unimportant in this mode.

BPU selects bits 2:0 should be set to indicate how much BPU-protected memory exists on the system. If no BPU is present, all three bits should be zero.

| Selected bit |      |      | Function               |  |  |

|--------------|------|------|------------------------|--|--|

| MMU2         | MMU1 | MMUo |                        |  |  |

| 0            | 0    | 0    | No MMU in system       |  |  |

| 0            | 0    | 1    | 1 Page Bank (PB0)      |  |  |

| 0            | 1    | 0    | 2 Page Banks (PB0-1)   |  |  |

| 0            | 1    | 1    | 4 Page Banks (PB0-3)   |  |  |

| 1            | 0    | 0    | 8 Page Banks (PB0-7)   |  |  |

| 1            | 0    | 1    | 16 Page Banks (PB0-15) |  |  |

| 1            | 1    | X    | 16 Page Banks (PB0-15) |  |  |

Note: In 1750A mode, setting any or all of the MMU select bits indicates the presence of an MMU.

Figure 5: MMU Selection Bits

#### 3.1.2. BUILT-IN TEST (BIT)

BIT consists of ten subroutines, as outlined in Figure 6. If all ten subroutines execute successfully, or no BIT is selected in the configuration word, a BIT pass is flagged (seen externally as NPU raised high by the initialization routine). If any part of BIT fails, a corresponding bit identifying the failed subroutine is set in General Register R0. Fault Bit 13 is set in the Fault register (FT) and NPU is left in the low state. Figure 6 defines the coding of BIT results in R0. In the event of such a failure, the resulting processor reset state will be dependent on where in BIT the error occurred and may not be the same as that shown in figure 2. A BIT failure indication in FT will set the level 1 interrupt request bit of the Pending Interrupt (PI) register. Since initialisation disables and masks interrupts, this interrupt request will not be asserted. Any external interrupts or faults occurring during BIT will be cleared before program execution begins and will not be serviced.

| Test Coverage                               | Machine<br>Cycles | Bit set<br>on fail |

|---------------------------------------------|-------------------|--------------------|

| Temporary Registers (T0-T11)                | 47                | 7                  |

| General Registers (R0-R15)                  | 79                | 7                  |

| Flags Block                                 | 18                | 8                  |

| Sequencer Operation and ROM checksum        | 5632              | 9 -                |

| Divide routine Quotient Shift<br>Network    | 12                | 10                 |

| Multiplier and ALU                          | 13                | 11                 |

| Barrel shift Network                        | 13                | 12                 |

| Interrupts and fault handling and detection | 17                | 13                 |

| Address generator block                     | 13                | 14                 |

| Instruction pipeline                        | 15                | 15                 |

Note: BIT pass is indicated by all zeros

in FT bits 13,14, and 15

Figure 6: Built-In Test Coverage

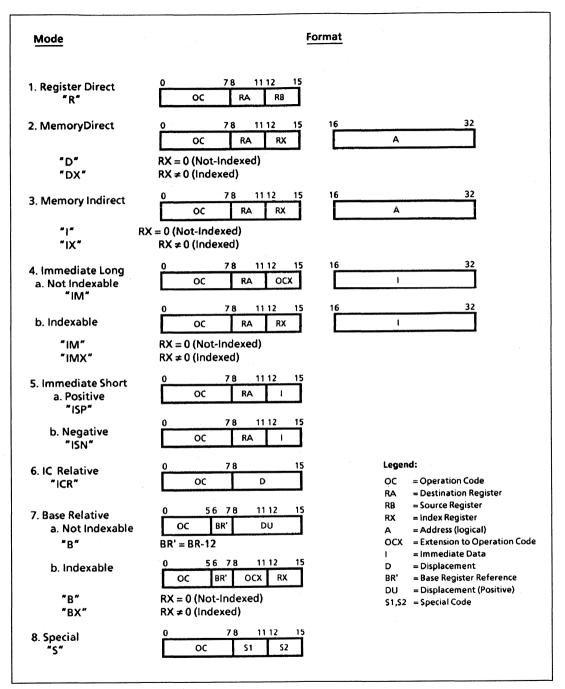

#### 3.2. INSTRUCTION EXECUTION

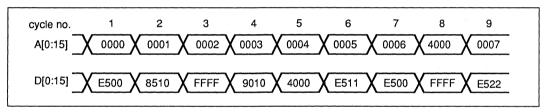

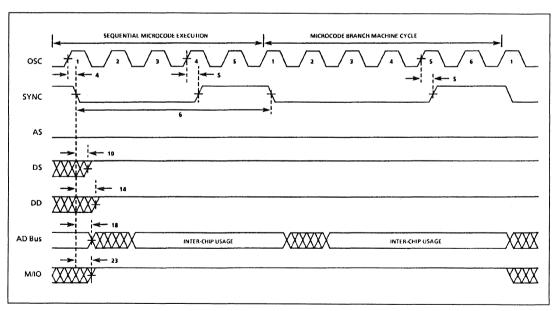

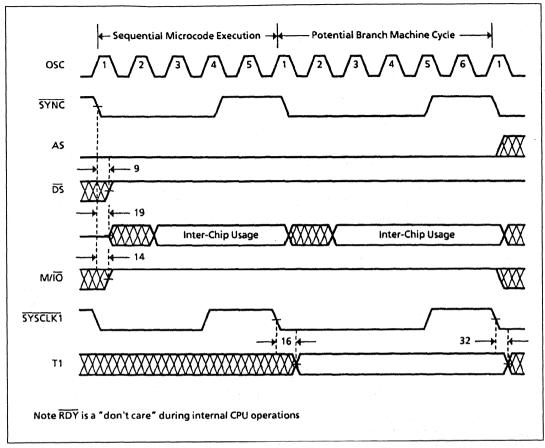

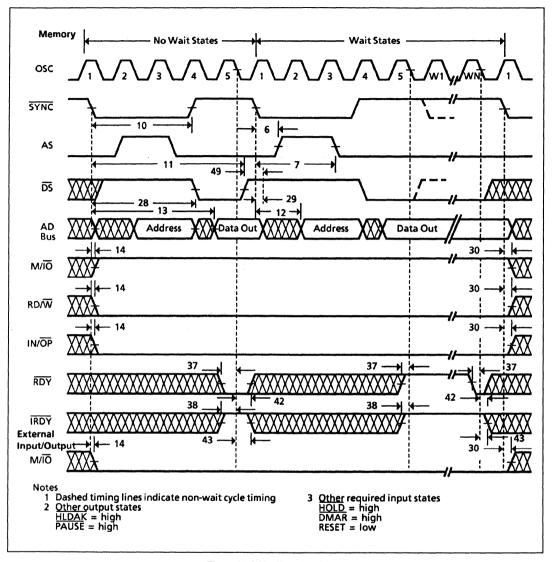

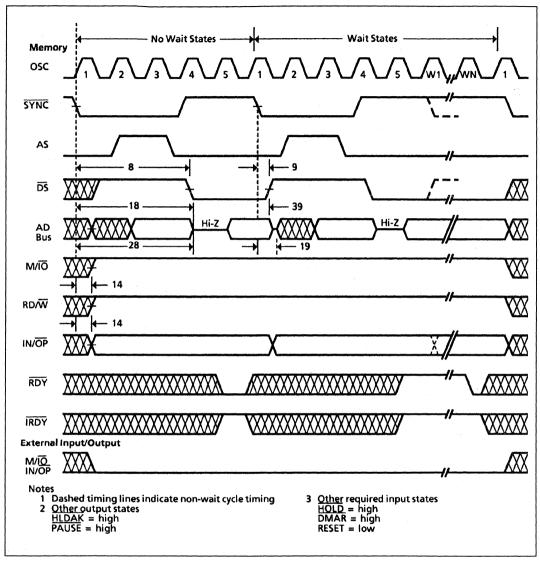

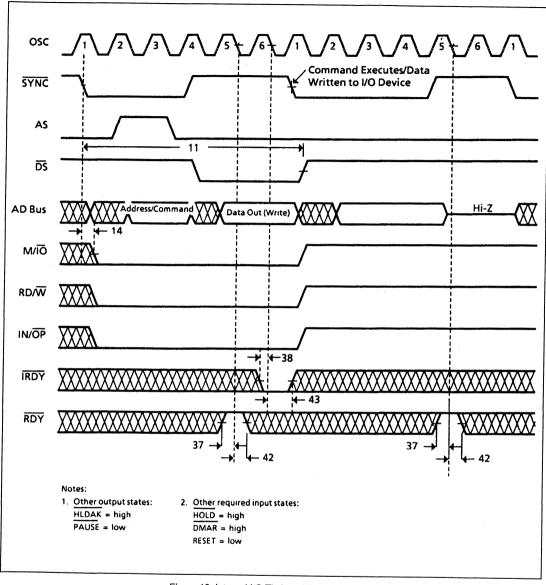

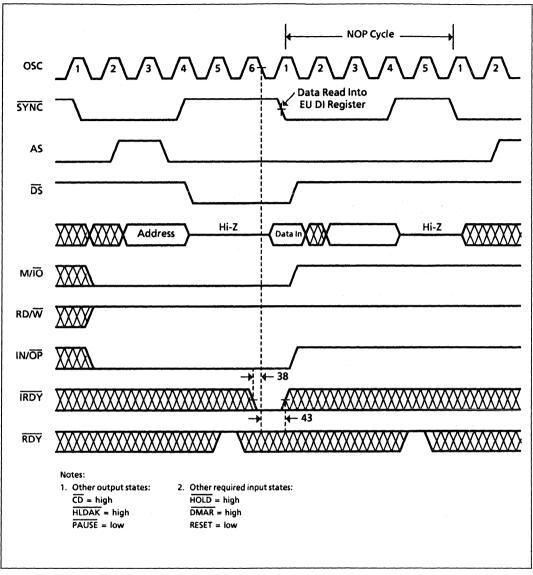

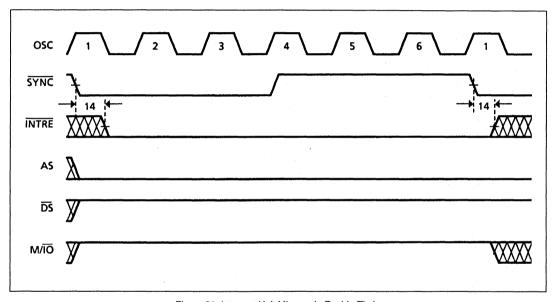

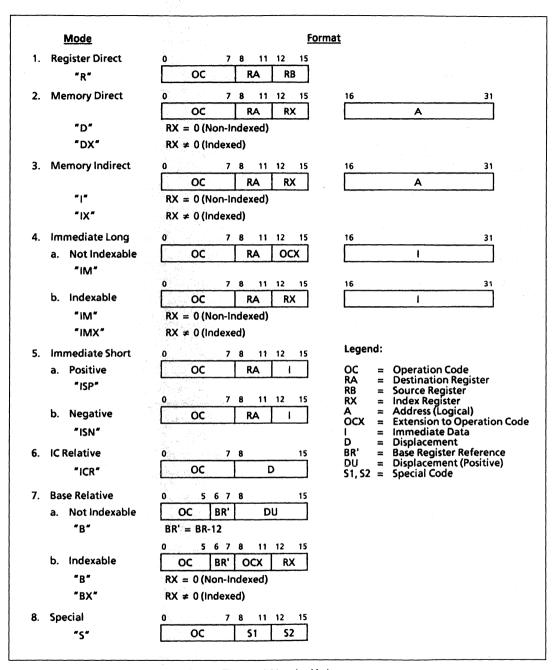

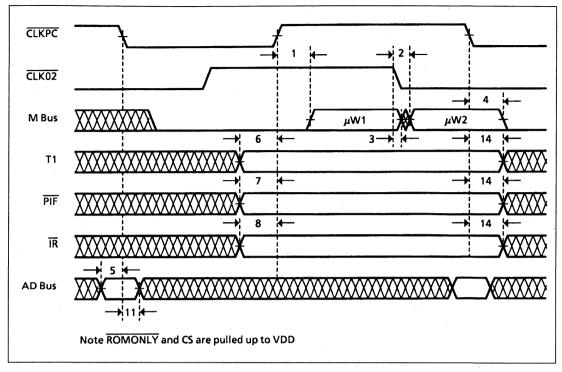

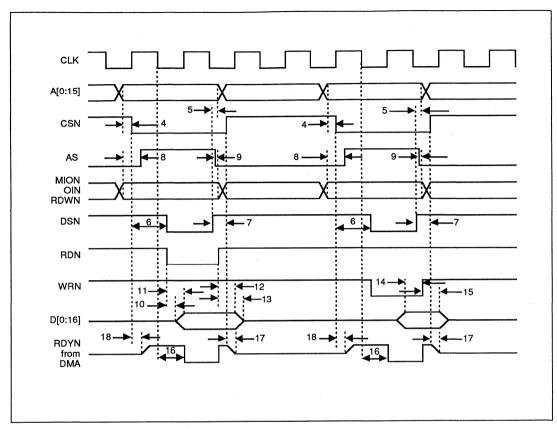

Once initialisation has been completed, the processor will begin instruction execution. Instruction execution is characterised by a variety of operations, each is one machine cycle in duration (two or more system CLK periods). Depending on the instruction being executed at the time, these operations include: (1) internal CPU cycles, (2) instruction fetches, (3) operand transfers, and (4) input/output transfers.

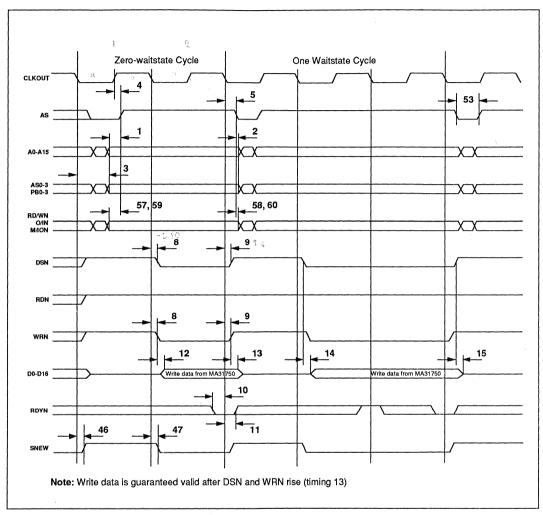

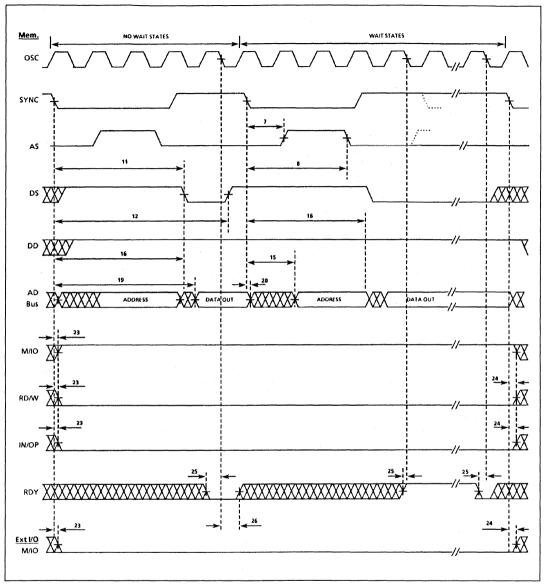

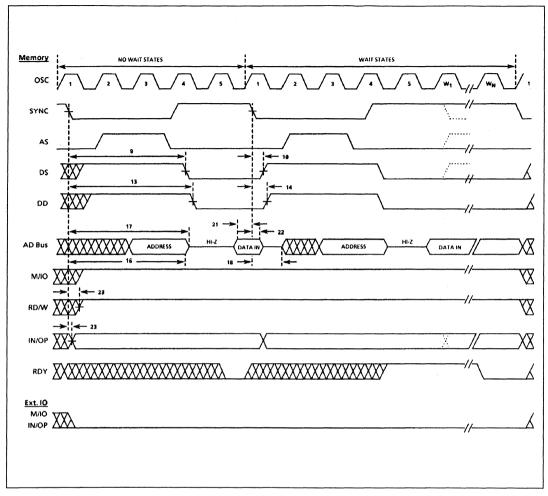

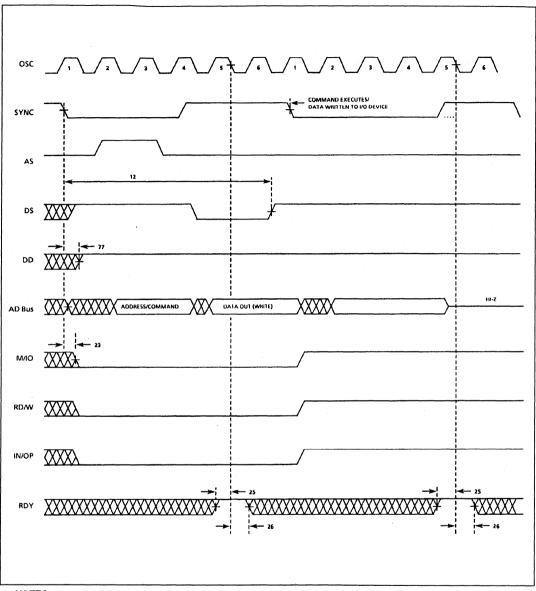

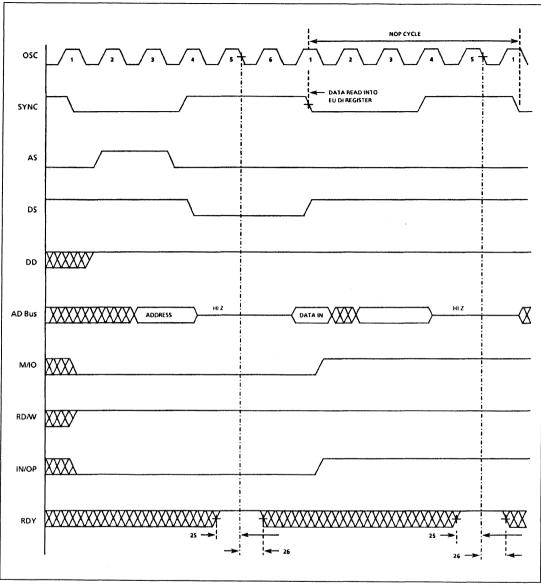

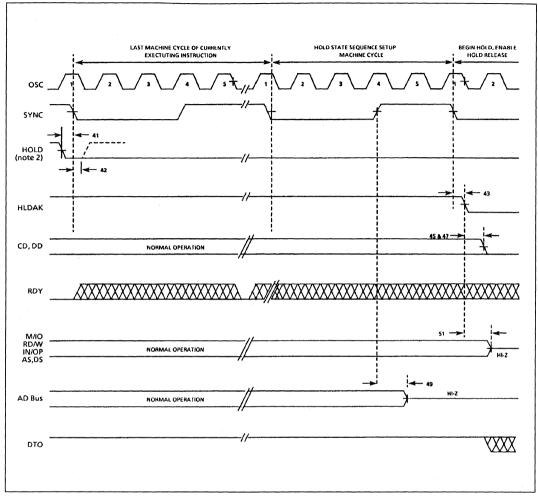

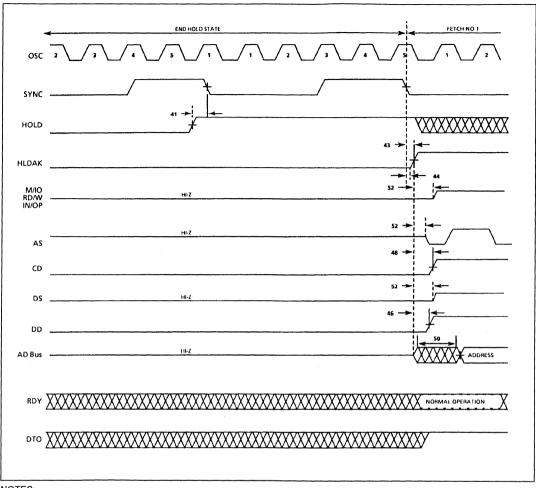

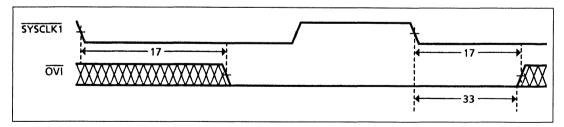

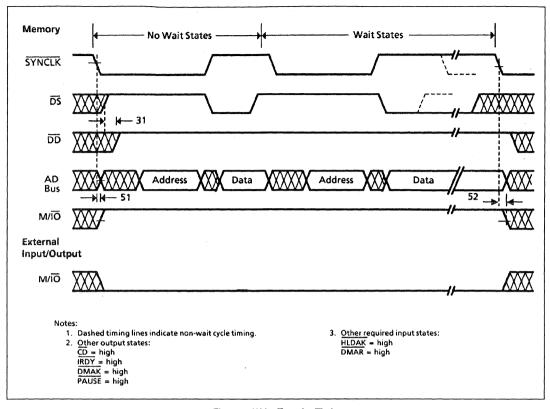

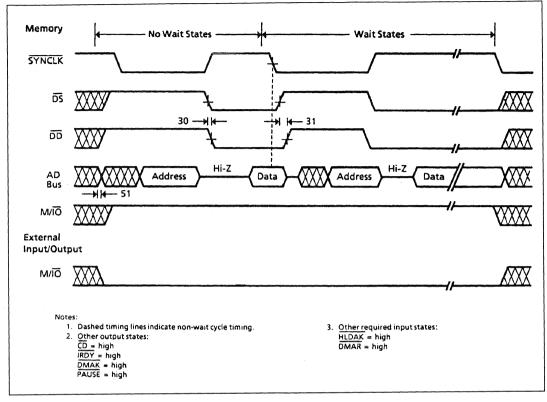

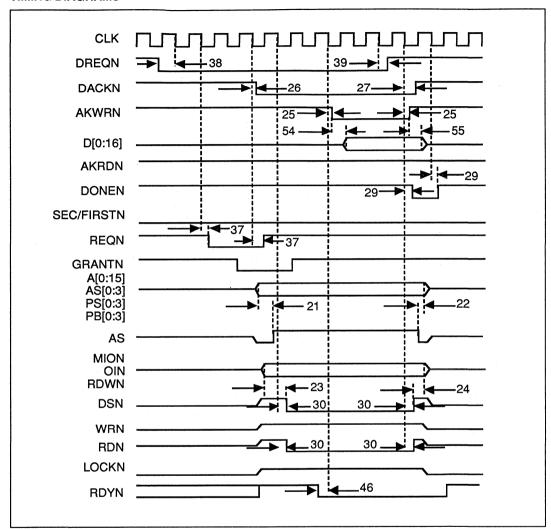

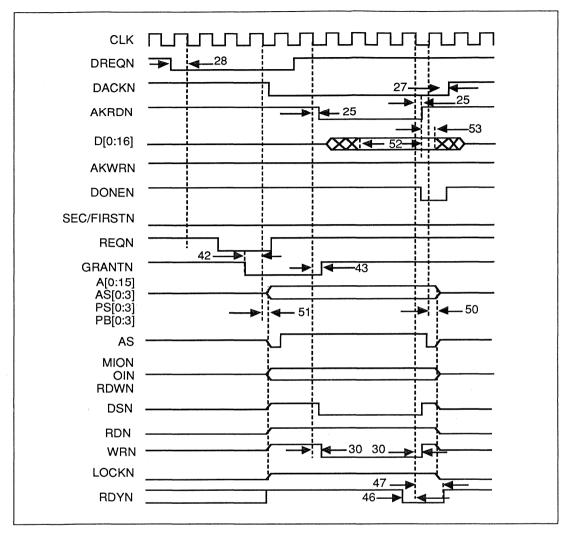

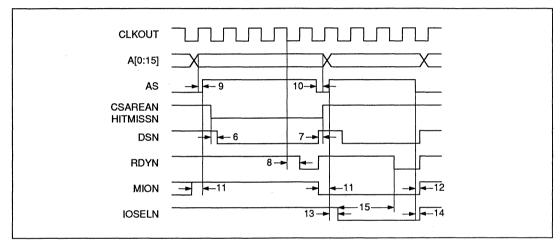

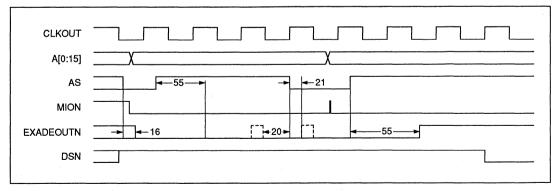

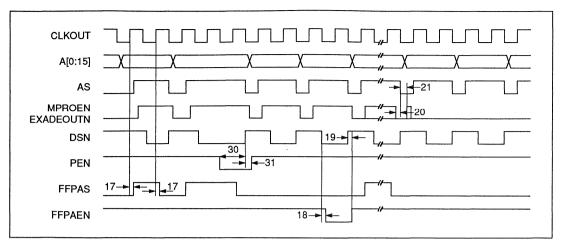

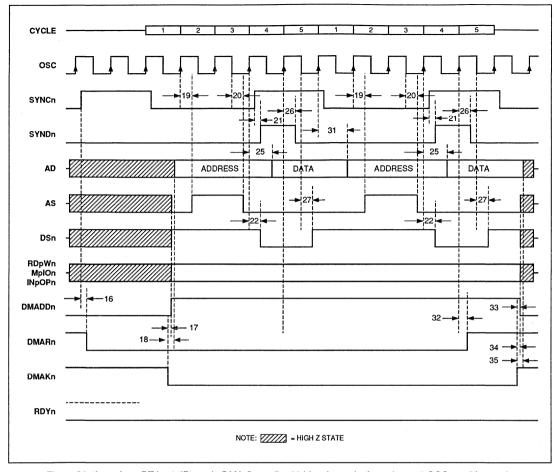

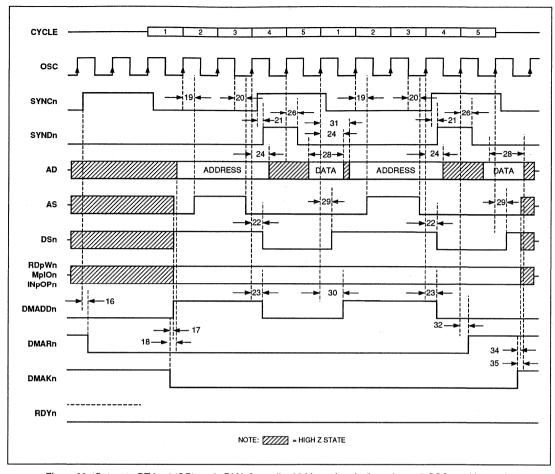

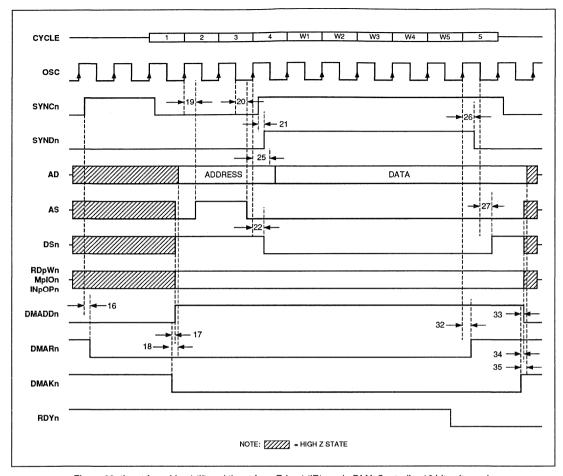

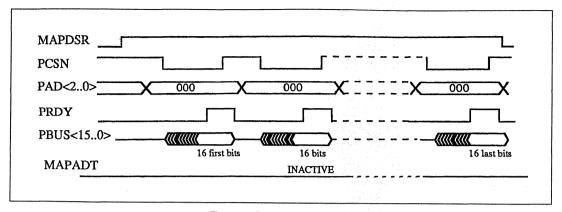

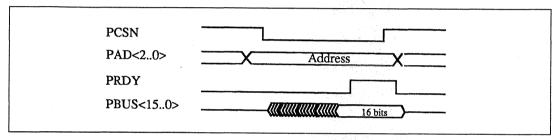

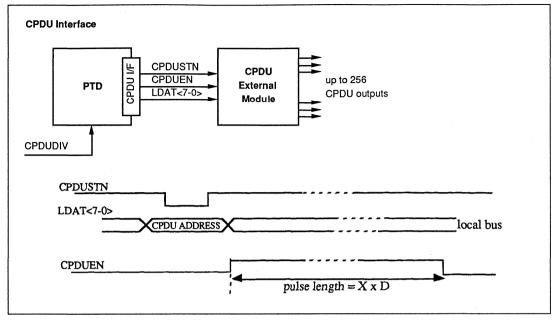

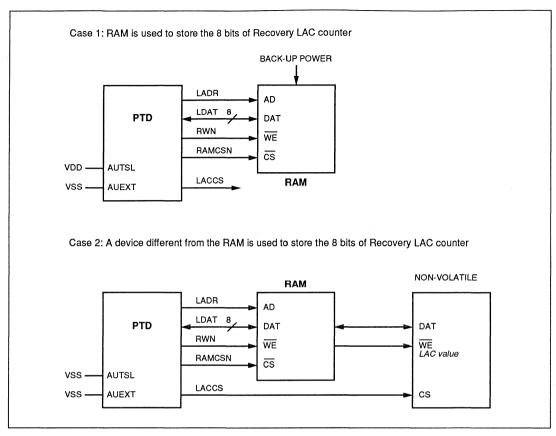

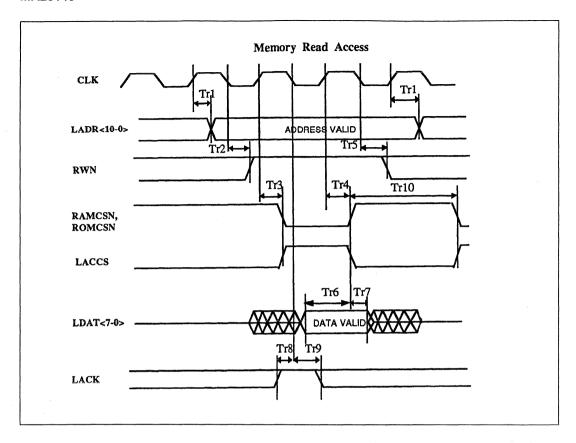

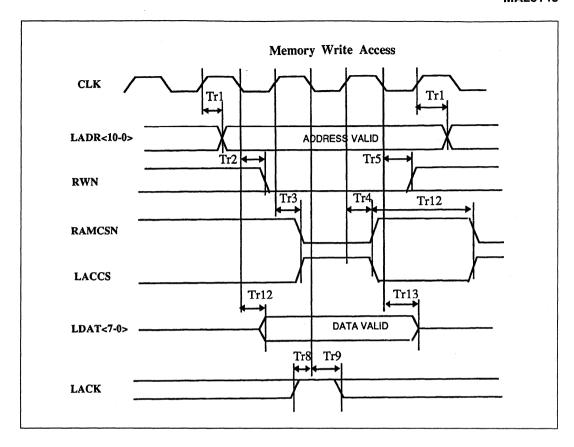

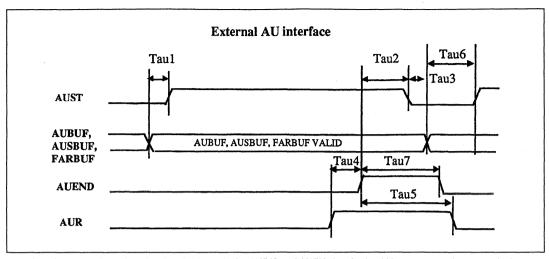

Instruction execution may be interrupted at the end of any individual machine cycle by an interrupt or Console request. Internal cycles are always two CLK periods long, whilst the other cycle types are a minimum of two CLK periods extendable by inserting waitstates. In all cycles except internal cycles, RDN, WRN, DSN and AS strobes are produced to control the transfer and latching of data and address around the system.

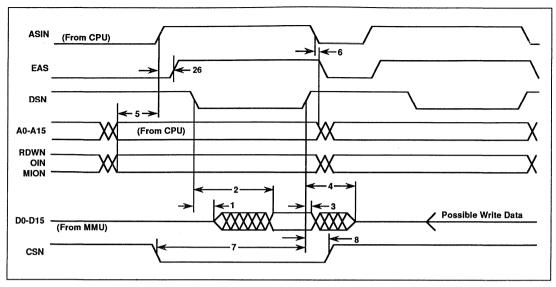

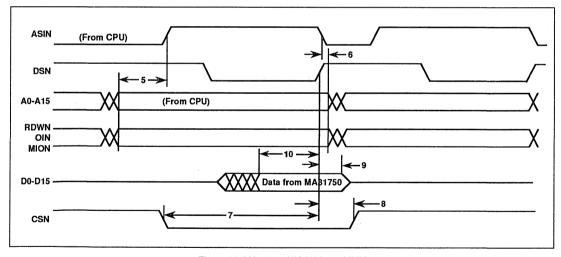

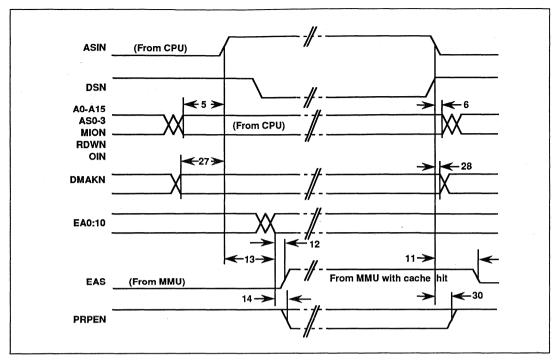

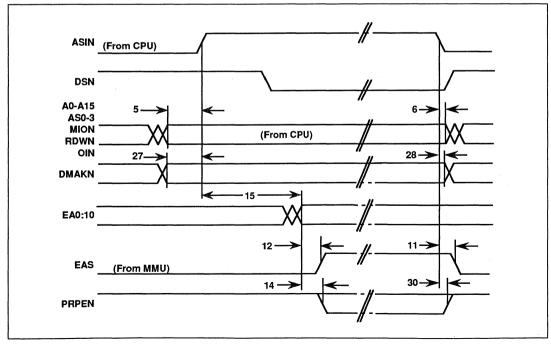

| Cycle Type                    | RD/WRN | O/IN   | M/ION  | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Internal Cycle                | Н      | L      | Н      | Used to perform all CPU data manipulation operations where bus activity is not required.                                                                                                                                                                                                                                                                                                                     |  |

| Instruction<br>Fetch          | Н      | L      | H      | Used to keep the instruction pipeline full with instructions and/or their postwords. At least one instruction is always ready for execution when the preceding instruction is completed. During jump and branch instruction execution the pipeline is refilled by two consecutive instruction fetches starting at the new instruction location. It is also refilled as part of interrupt request processing. |  |

| Operand Read<br>Operand Write |        | H      | H<br>H | Used to read in data from the external system and to write results to the system.                                                                                                                                                                                                                                                                                                                            |  |

| IO Read<br>IO Write           | H<br>L | H<br>H | L      | Input/Output transfers utilize the MIL-STD-1750 XIO and VIO instructions. RD/WN defines the direction of the transfer. IO tran may be divided into three groups; those commands which are implemented internally by the CPU, those commands which are implemented by external system hardware and those commands defined as illegal by MIL-STD-1750A and B.                                                  |  |

Figure 7: External Cycle Types

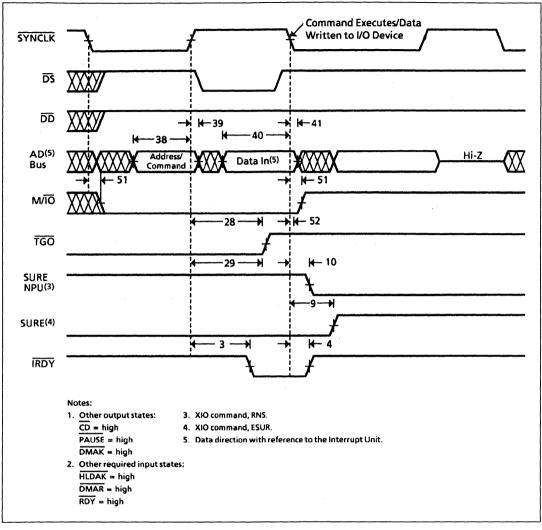

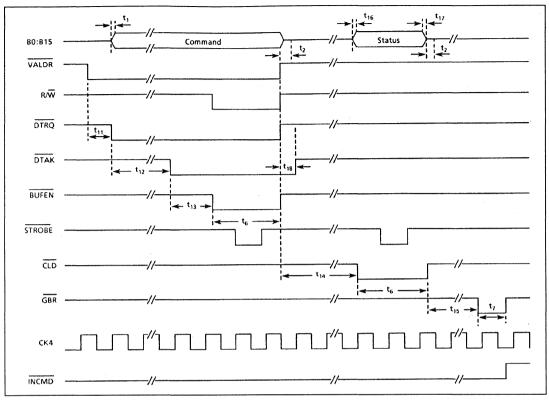

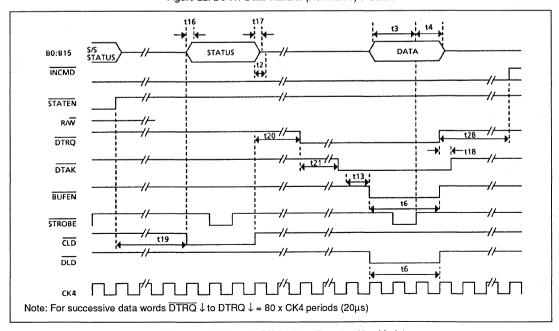

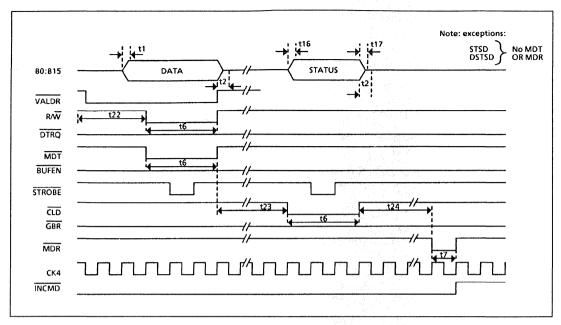

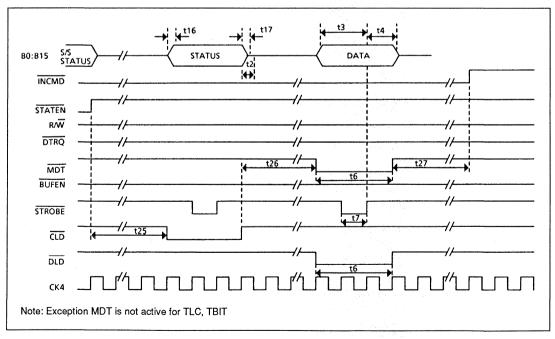

#### 3.3. IO OPERATION

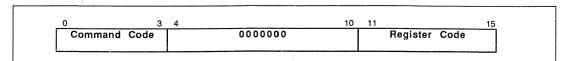

The MA31750 supports a 64KWord addressing space dedicated to IO control and communication in accordance with MIL-STD-1750. The control line MION is asserted low when accessing IO space (see figure 7 above for other strobe states). One of the two commands XIO or VIO is used to specify both data for the transfer and the port address (referred to as an XIO Command in 1750). The CPU contains logic which decodes all internally supported XIO commands and generates the control signals necessary to carry out the commanded action. In addition, the validity of a command not implemented internally is verified. Figure 20c identifies the XIO commands which are internally supported by the MA31750.

#### 3.4. INTERRUPT AND FAULT HANDLING

#### 3.4.1. STATUS WORD (SW)

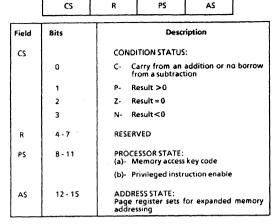

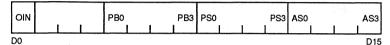

Figure 8 depicts the status register format. This 16-bit word is divided into four, 4-bit sections. Three of these sections [AS, PS and, (1750B mode) PB] are control bits for implementing expanded memory with an external MMU. The fourth section, CS, is used to hold the carry, positive, zero and negative condition flags set by the result of the previous arithmetic operation.

| 0 3 | 4 7    | 8 11 | 12 15 |

|-----|--------|------|-------|

| CS  | R (PB) | PS   | AS ,  |

| Field   | Bits             | Description                                                                                                           |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| CS      | 0<br>1<br>2<br>3 | CONDITION STATUS C- Carry from an addition or no borrow from a subtraction. P- Result > 0 Z- Result = 0 N- Result < 0 |

| R<br>PB | 4-7              | RESERVED (=0) in 1750A mode<br>Page Bank Select in 1750B mode                                                         |

| PS      | 8-11             | PROCESSOR STATE:<br>(a)- Memory access to key code<br>(b)- Priviledged instruction enable                             |

| AS      | 12-15            | ADDRESS STATE:<br>Page register sets for expanded<br>memory addressing.                                               |

Figure 8: Status Word Format

#### MA31750

The AS field is used during expanded memory access to define the page register set to be used for instruction and operand memory references. The PS field is used during memory protect operations to define the access key used for memory accesses. The PS field is also used during execution of privileged Instructions - PS must be zero for such operations to be legal. See Section 4.3 for further information on the use of this field. The PB field is used in conjunction with the AS field in 1750B mode to expand the number of page registers available. Note that attempting to set AS or PB to a non-zero value with no MMU, or setting PB to a non-zero value in 1750A mode is illegal. This will be aborted and a fault 11 will be generated (SW will remain unchanged).

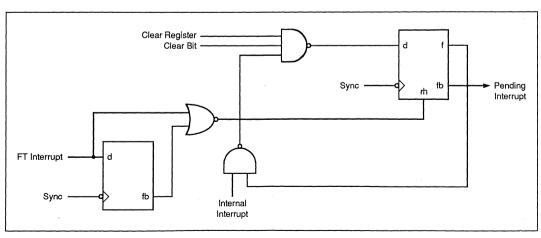

#### 3.4.2. PENDING INTERRUPT REGISTER (PI)

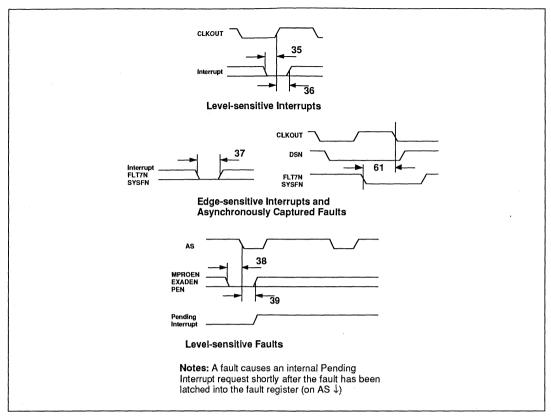

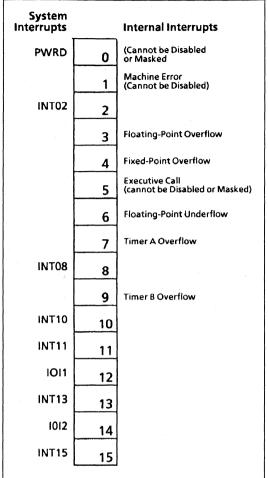

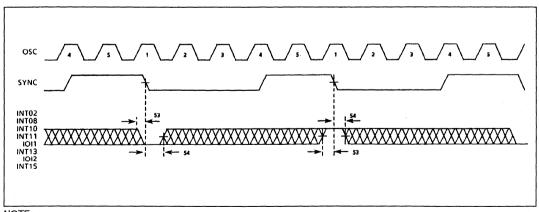

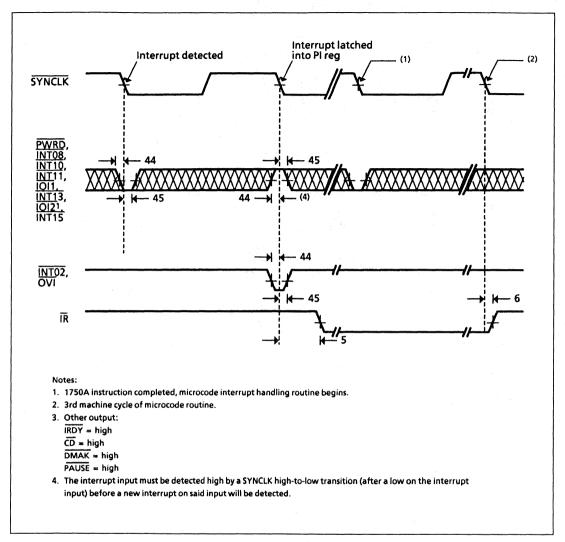

This 16-bit register is used to capture and hold interrupts until they can be processed by microcode and user software. A logic 1 is used to represent an active pending interrupt. The PI register supports three dedicated external, six user-definable external, and seven dedicated internal interrupts. Levelsensitive interrupts are sampled on each rising CLK edge, whilst edge sensitive interrupts are captured immediately.

|       |    | Internal<br>Interrupts                        |                                         |     | Internal<br>Faults         |

|-------|----|-----------------------------------------------|-----------------------------------------|-----|----------------------------|

| PWRD  | 0  | (Cannot be disabled or masked)                | MPROE (CPU)                             | 0   |                            |

|       | 1  | Machine Error (Cannot be disabled)            | MPROE (DMA)                             | 1   | ·                          |

| INT02 | 2  |                                               | PE (CPU memory)                         | 2   |                            |

|       | 3  | Floating-Point Overflow                       | PE (CPU IO)                             | 3   |                            |

|       | 4  | Fixed-Point Overflow                          | PE (DMA)                                | 4   |                            |

|       | 5  | Executive call (Cannot be disabled or masked) | EXADE or Bus<br>Timeout (CPU IO)        | - 5 |                            |

|       | 6  | Floating-Point Underflow                      | ,                                       | 6   | Parallel IO Transfer Error |

|       | 7  | Timer A Overflow                              | FLT7                                    | . 7 |                            |

| INT08 | 8  |                                               | EXADE or Bus<br>Timeout (CPU<br>memory) | 8   |                            |

|       | 9  | Timer B Overflow                              |                                         | 9   | Illegal Instruction Opcode |

| INT10 | 10 |                                               |                                         | 10  | Priviledged Instruction    |

| INT11 | 11 |                                               |                                         | 11  | Unimplemented Address Sta  |

| IOI1  | 12 |                                               | Reserved                                | 12  |                            |

| INT13 | 13 |                                               | SYSF                                    | 13  | MA31750 BIT Fail           |

| 1012  | 14 |                                               | EXADE (DMA)                             | 14  |                            |

| INT15 | 15 |                                               | SYSF                                    | 15  |                            |

Figure 9: Pending Interrupt Bit Assignments

Figure 10: Fault Register Bit Assignments

#### 3.4.3. MASK REGISTER (MK)

This 16-bit register is used to store the interrupt mask. Interrupts are masked by ANDing each mask bit with its corresponding PI register bit. ie. A logic zero in a given bit position indicates that the corresponding bit in the PI register will be masked. Interrupts which are masked will be captured in the PI register but will not be acted on until unmasked. Interrupt level zero can not be masked.

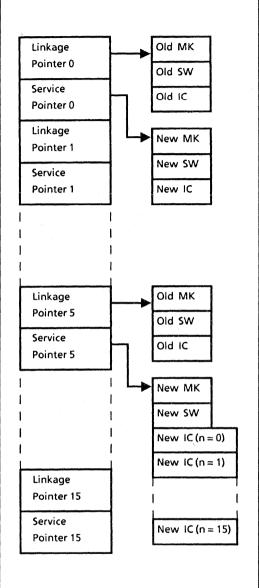

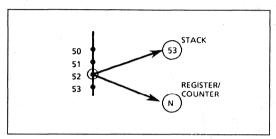

#### 3.4.4. PRIORITY ENCODER

This encoder generates an interrupt request to the sequencer block whenever one or more unmasked interrupts are pending and enabled in the Pl. The highest priority unmasked pending interrupt is encoded as a 4-bit vector. This vector is used during interrupt servicing in order to create the interrupt linkage and service pointers.

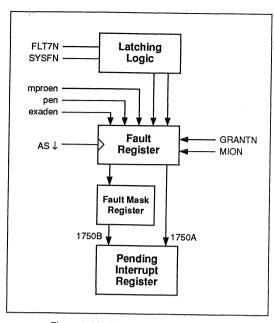

#### 3.4.5. FAULT REGISTER (FT)

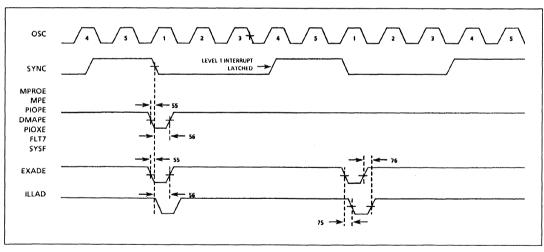

This 16-bit register is used to capture and hold both internal and user implemented external faults using positive logic, i.e., a logic one represents a fault. Bus cycle faults are captured at the end of each machine cycle whilst the two general purpose faults SYSFN and FLT7N are set when the low time exceeds the minimum pulse width. Setting any one or more faults in FT will cause a level 1 (machine error) interrupt request. Once a fault is set in FT, it may only be cleared via an XIO command.

In 1750B mode, a fault mask register is provided to allow selective masking of fault conditions. Section 4 (Software Considerations) contains further information. Figure 27 shows the fault register assignments.

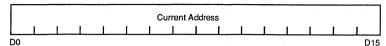

#### 3.4.6. MEMORY FAULT PAGE AND ADDRESS REGISTERS

These registers capture the page and address information at the end of each external cycle until a memory fault occurs. Faults setting bits 0, 1, 2 and 8 in the fault register cause the registers to stop latching new address information, so retaining information about the address at which the fault occured. The registers can be read (using the GPS defined XIOs RMFP and RMPA). The fault register must be cleared and both memory fault registers read before latching can restart.

The information stored in the memory fault registers is as follows:

| MFPR[0:3]              | <b>MFPR[4:7]</b>      | MFPR[8:10 | ION                            |

|------------------------|-----------------------|-----------|--------------------------------|

| A[0:3]                 | PB[0:3](ASOB)         | Res       |                                |

| MFPR[12:15]<br>AS[0:3] | MFAR[0:15]<br>A[0:15] |           | MFPR[11] is the overse of OIN. |

These registers are only available if there is an MMU in the system. If there is no MMU present, then the RMFP and RMFA XIO commands become illegal.

The address information held in these registers can be used to restart code after a memory fault has occurred. Bits [6:7] of the OAS register store information on the type of instruction which was being executed when the fault occured:

$00 \rightarrow$  branch that was taken

01 → single word instruction

10 → double word instruction

(Subtracting this value from the saved address will give the address of the failed instruction unless it was a branch that was taken).

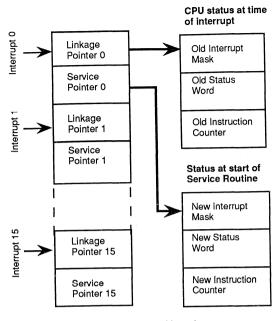

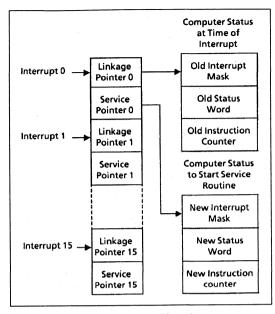

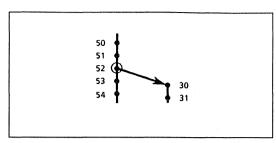

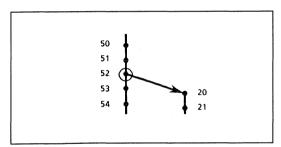

Figure 11: Interrupt Vectoring

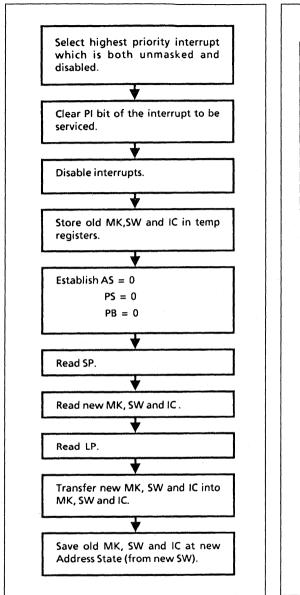

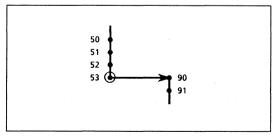

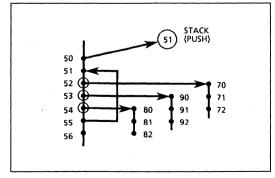

#### 3.4.7. INTERRUPT SERVICING

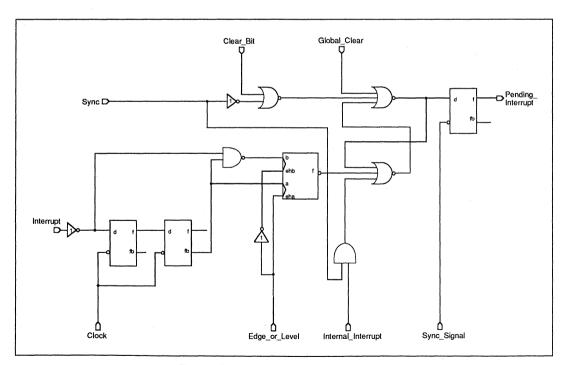

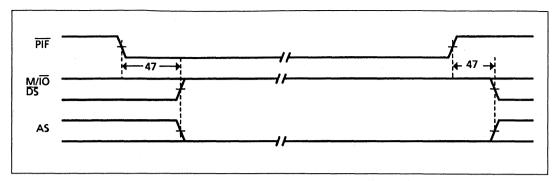

Nine user interrupt request inputs are provided for programmed response to asynchronous system events. A low on any of these inputs will be detected at the rising edge of CLK (level sensitive interrupts only) and latched into the Pending Interrupt (PI) register on the falling edge of CLK at the end of the current CPU cycle. This sequence occurs whether interrupts are enabled or disabled or whether the specific interrupt is masked or unmasked. More details of interrupt operations are available in Applications Note 4.

All of the user interrupts PWRDN, INT02N - INT15N may be programmed to be either level or edge sensitive by setting or clearing the appropriate bit in the system configuration register. If edge sensitivity is selected then an interrupt request input must return to the high state before a subsequent request on that input will be detected. If level sensitivity is selected then holding an interrupt input low will cause a new interrupt to be latched following each service. Note that interrupts IOI1N and IOI2N are level sensitive only.

In order that the system may recognise when a service has been started, an interrupt acknowledge pin is provided. During the microcoded interrupt service routine execution, the processor will read the Linkage Pointer address in memory. During this operand read cycle, the processor will also assert INTAKN low, which may be used in conjunction with AS and address bus bits A[11:14] to reveal the priority level of the interrupt being serviced. (A[11:14] = 0 indicates level 0 interrupt, A[11:14] = 1 indicates level 1 interrupt, and so on). INTAKN should also be used to remove level-sensitive interrupt requests to ensure that repeated requests are not generated.

|          | Interrupt<br>No. | LP<br>Address | SP<br>Address |

|----------|------------------|---------------|---------------|

| PWRD     | 0                | 20            | 21            |

| ME       | 1                | 22            | 23            |

| INT02    | 2                | 24            | 25            |

| FI.P o/f | 3                | 26            | 27            |

| Fx.P o/f | 4                | 28            | 29            |

| BEX      | 5                | 2A            | 2B            |

| FI.P u/f | 6                | 2C            | 2D            |

| Timer A  | 7                | 2E            | 2F            |

| INT08    | 8                | 30            | 31            |

| Timer B  | 9                | 32            | 33            |

| INT10    | 10               | 34            | 35            |

| INT11    | 11               | 36            | 37            |

| IOI1     | 12               | 38            | 39            |

| INT13    | 13               | ЗА            | 3B            |

| 1012     | 14               | 3C            | 3D            |

| INT15    | 15               | 3E            | 3F            |

Note: Addresses (in hex) are in operand space

Figure 12: Interrupt Pointer Address

When an interrupt request is latched into PI, it is ANDed with its corresponding mask bit in the mask register (MK). NOTE: Interrupt level 0 is non-maskable. Any unmasked pending interrupts are output to the priority encoder where the highest priority is encoded as a 4-bit vector. If interrupts are enabled and an unmasked interrupt is pending, the priority encoder will assert an interrupt request to the sequencer. 1 or 2 extra CLKs will be inserted into the machine cycle on which the interrupt request is asserted.

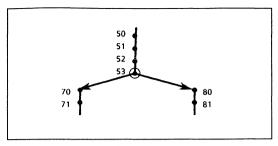

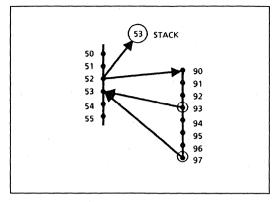

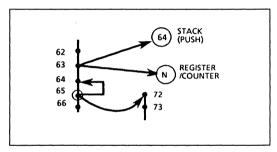

Upon completing execution of each MIL-STD-1750A or B instruction, the sequencer checks the state of the priority encoder interrupt request. If a request is asserted, the sequencer branches to the microcode interrupt service routine. This routine reads the 4-bit pending interrupt vector and then uses this value to calculate the appropriate interrupt linkage (old processor context save area) and service (new context load area) pointers. Figure 11 depicts this relationship. Figure 12 defines the pointer values.

Using the linkage and service pointers, the microcode interrupt service routine performs the following: (1) the current contents of the status word, mask register, and instruction counter are saved; (2) a write status word (WSW) I/O command is executed with an all zero data word; (3) the new mask is loaded into MK and interrupts are disabled; (4) the new status word is read and checked for a valid Address State (AS[0:3]) field - If the address state is non-zero and an MMU is not present, AS[0:3] is set to zero and fault 11 (address state error) is set in the fault register FT); (5) a write status word command using the new status word is performed; and (6) the new IC value is loaded into IC, the instruction pipeline is flushed and refilled starting at the new address, and instruction execution begins.

[NOTE: The steps listed above represent a summary of actions performed during interrupt servicing and do not necessarily reflect the actual order in which these events take place.]

If an address state fault occurs during the service routine, interrupt level 1 will be set. This interrupt will be serviced when interrupts are re-enabled unless it is masked by the new value in MK.

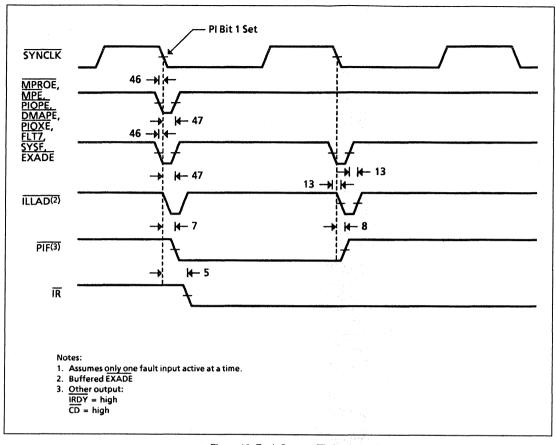

#### 3.4.8. FAULT SERVICING

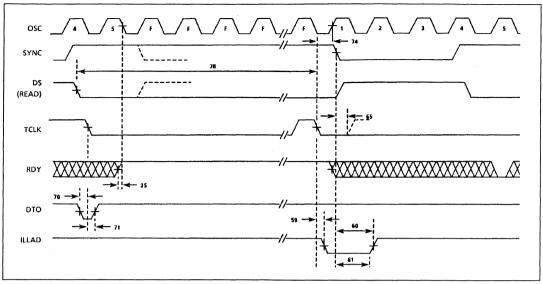

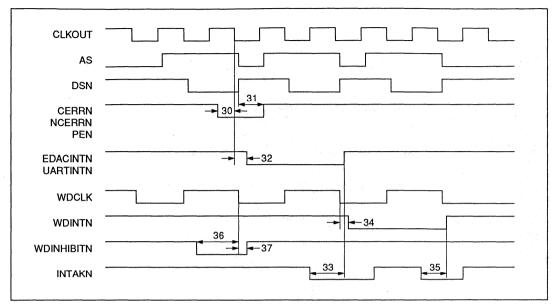

Five user fault inputs are provided. A low on any of the three bus-cycle-related fault inputs, EXADEN, MPROEN or PEN, will be latched into the Fault Register (FT) on the next falling edge of AS. A low on either of the two general purpose fault inputs, FLT7N or SYSFN, will be latched immediately and will be sampled into the appropriate bit of FT on the falling edge of AS.

Any fault which sets a bit in the FT immediately causes a level 1 pending interrupt to be entered into the PI register. This interrupt is maskable but may not be disabled.

This interrupt will be serviced at the end of the currently executing 1750 instruction if not masked. The microcoded interrupt service routine reads the interrupt priority vector and clears the bit relating to the serviced interrupt from the Pl. However, the FT retains the set fault bits until the FT is cleared using the XIO RCFR command. (A non-destructive read of the FT is provided by the XIO RFR command.) Anti-repeat logic between the FT and the Pl prevents the same fault being latched and serviced twice. However, as all FT bits are ORed together and input to Pl bit 1, this also prevents any other faults being serviced until the fault register has been cleared. It is imperative, therefore, that the fault service routine executes a RCFR XIO before exiting. Different types of faults are serviced slightly differently as follows:

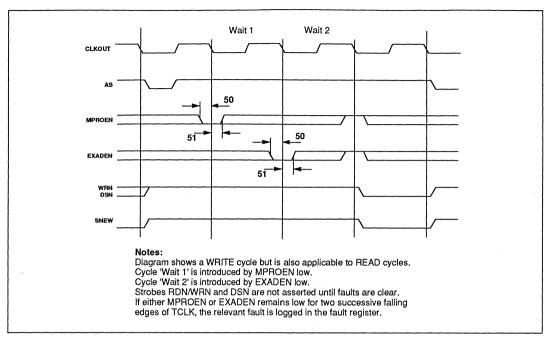

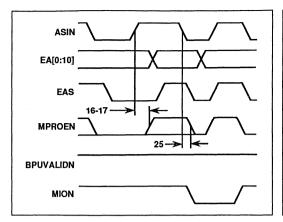

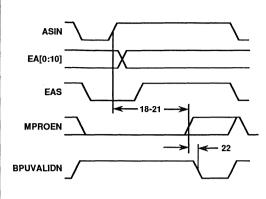

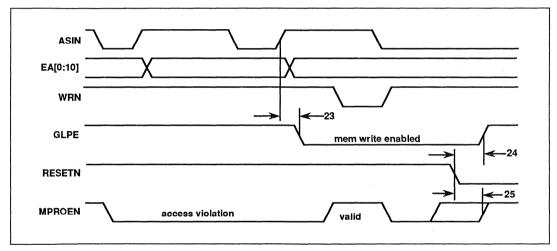

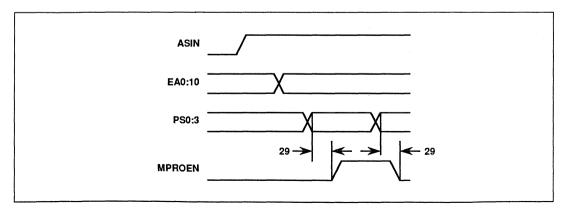

#### 3.4.8.1. MPROEN and EXADEN

If MPROEN and/or EXADEN are low on a falling clock edge with AS and DSN high (see figure 23a), the processor will wait in this state. If either fault input remains low during two falling edges of TCLK, the cycle is forced to complete but RDN/WRN and DSN are inhibited (see figure 24b). This allows the processor to prevent erroneous accesses. An access fault will be registered as AS falls at the end of the cycle.

#### 3.4.8.2. PEN

External parity errors are latched into the FT on the falling edge of AS. The fault bit set is dependent upon the type of transfer taking place (memory, IO or DMA).

#### 3.4.8.3. FLT7N and SYSFN

These faults are latched immediately, but are not sampled into the fault register until the following falling edge of AS.

#### 3.4.9. PARITY GENERATION AND CHECKING

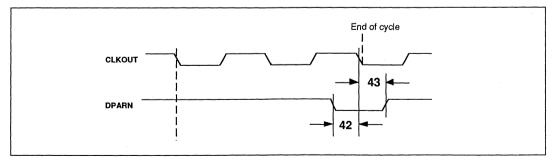

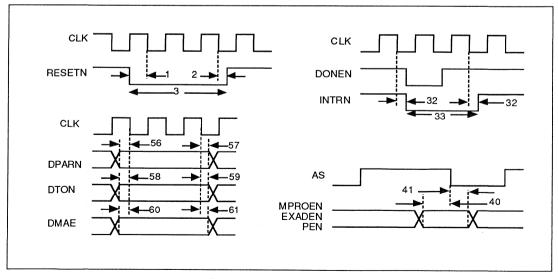

The MA31750 features on-chip parity generation and checking on all data bus transfers. Data generated by the processor has a parity bit attached to it to allow external logic to verify write transfers. On read transfers, the processor will check the incoming parity (if enabled) and will generate the appropriate parity error fault if detected. However, the data to be checked is only available as DSN rises at the end of the cycle so the error flag is generated and latched in the cycle following the erroneous cycle. Parity checking may be

disabled when operating with devices which do not support parity generation by asserting the DPARN (Disable Parity) input low. The checking polarity (odd or even) is selectable with Configuration Register bit 6.

#### 3.5. TIMER OPERATIONS

The MA31750 implements interval timers A and B, a trigger-go counter, and a bus fault timer. A discussion of each follows:

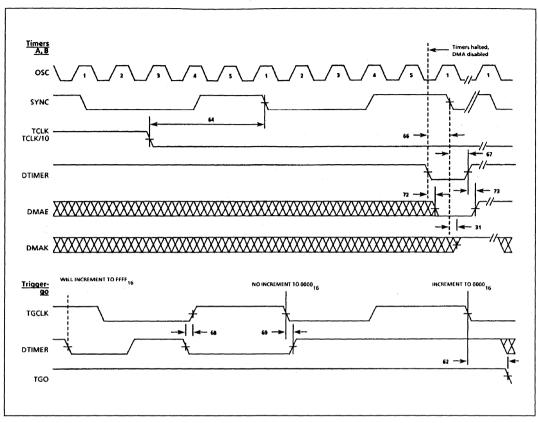

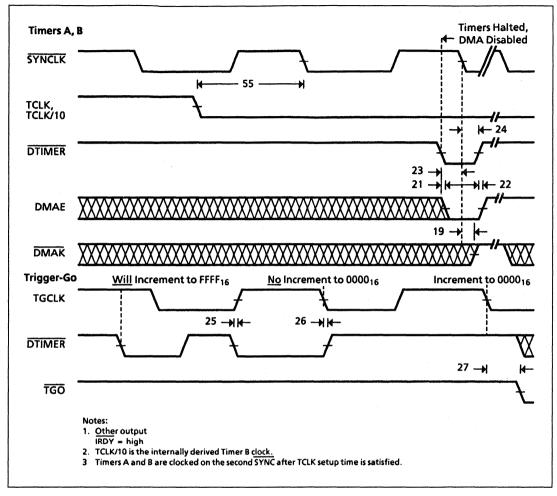

#### 3.5.1. TIMERS A AND B

Two general-purpose, 16-bit timers are provided in the processor. Timer A is clocked by the TCLK input; timer B is clocked by an internally generated TCLK/10. The divider circuit is reset when Timer B is reset to give deterministic processor operation. MIL-STD-1750 requires TCLK to be a 100kHz pulse train. If allowed to overflow, timers A and B will set level 7 and level 9 interrupt requests respectively. Each timer can be read, loaded, started and stopped by using XIO commands as identified in figure 20c.

Each timer has associated with it a reset register from which the timer is automatically loaded following a software reset or overflow. These registers are initially loaded with zero but may be reloaded from software (using the XIO instructions OTA and OTB) to provide greater control over the count period.

The MA31750 timers A and B will be disabled when the device enters Console mode, as required by MIL-STD-1750A Notice 1.

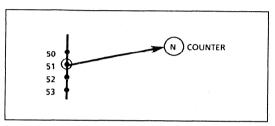

#### 3.5.2. TRIGGER-GO COUNTER

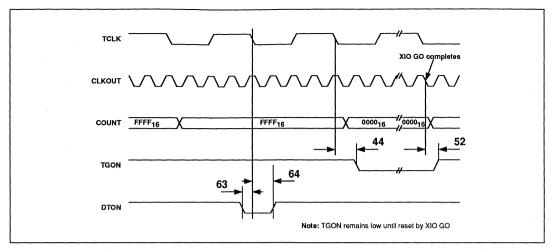

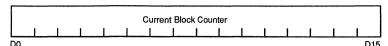

This 16-bit counter is clocked by the TCLK input and is typically used as a system "watchdog" timer. It is enabled during system initialisation and may be preset under software control to give a wide range of timeout intervals. In order that the count period may be controlled, a reset register is provided. On reset, this register is loaded with zero, but can be reloaded under software control to take any value between 0 and FFFF<sub>1e</sub> (a value of zero gives the maximum count period). This allows the timeout period to be varied between 20us and 0.65s. Note that there is no value which disables the timer.

The counter is incremented on each TCLK falling edge. Whenever the trigger-go counter overflows, TGON drops low and remains low until the counter is reloaded from the reset register via the GO internal XIO command. TGON low would typically be used to initiate a user-defined system recovery action such as a system reset.

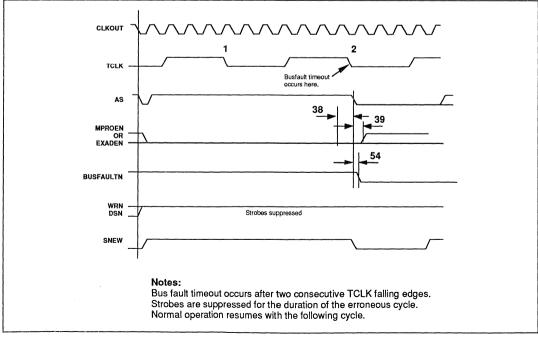

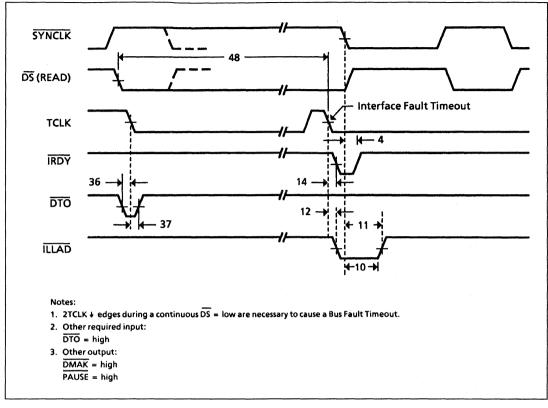

#### 3.5.3. BUS FAULT TIMER

All bus operations are monitored to ensure timely completion. A hardware timeout circuit is enabled at the start of each memory and I/O transfer (DSN high-to-low transition) and is reset upon receipt of the external ready (RDYN) signal. If this circuit fails to reset within a minimum of one TCLK period or a maximum of two TCLK periods, either bit 8 (if the transaction is with memory) or bit 5 (if the transaction is with I/O) of the Fault Register (FT) is set. This sets Pending Interrupt level 1 and causes the strobes to be suppressed and the current bus cycle to be aborted. The MIL-STD-1750 instruction is aborted, and control passes to the level 1 interrupt service routine (if the level 1 interrupt is unmasked). The timeout mechanism is disabled and reset if DTON is asserted low.

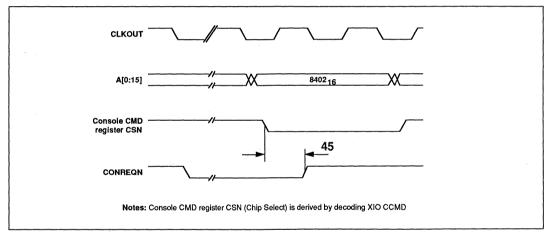

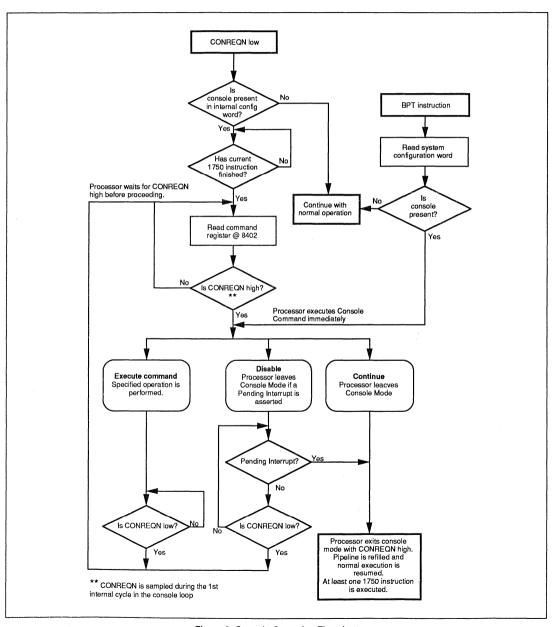

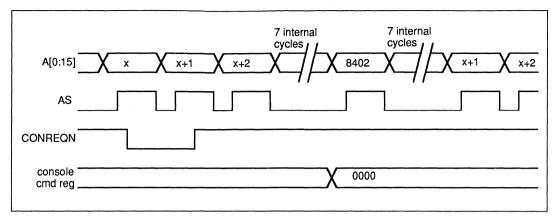

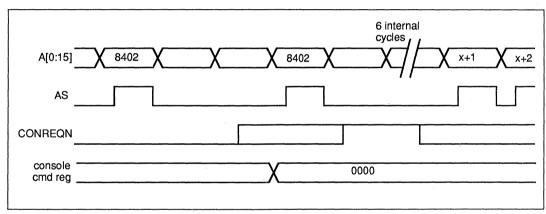

#### 3.6. CONSOLE OPERATION

The MA31750 is capable of interfacing directly to an external console, allowing the developer to: examine and change the contents of internal registers, memory and IO devices; single step code and halt the processor. Applications Note 3 provides a full description of the Console interface, its implementation and operation.

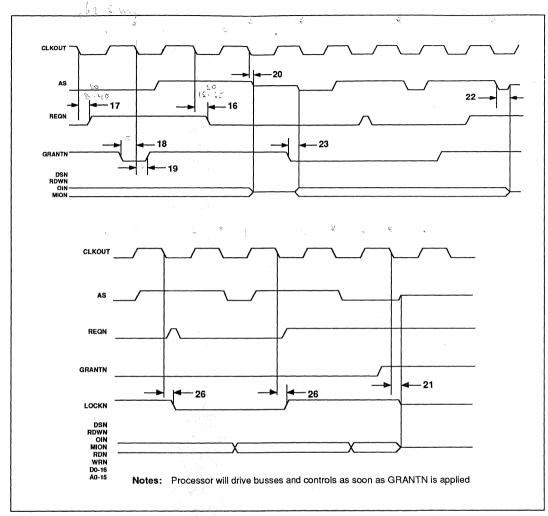

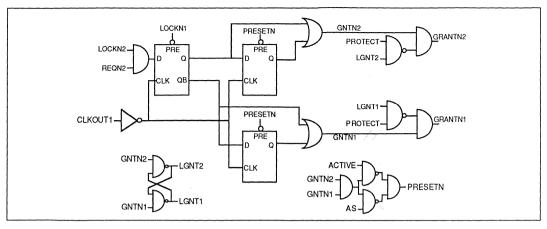

#### 3.7. MULTIPROCESSOR SUPPORT

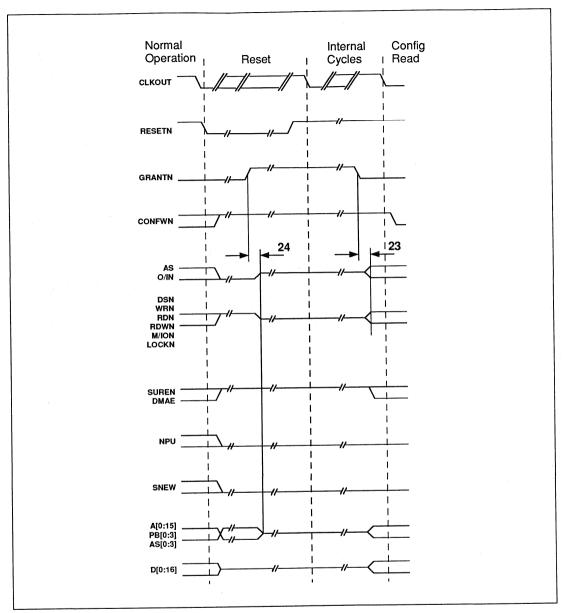

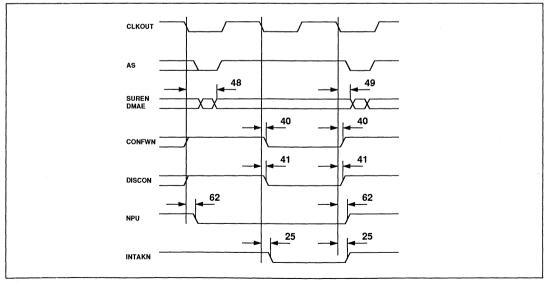

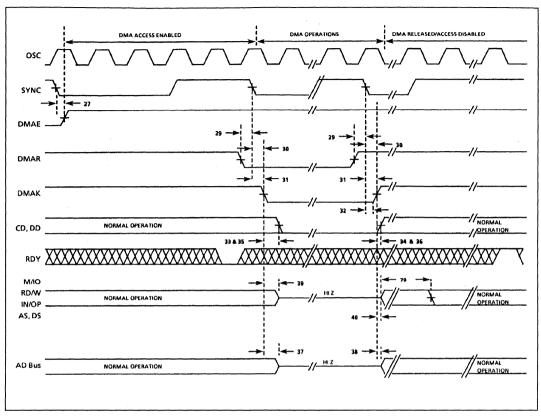

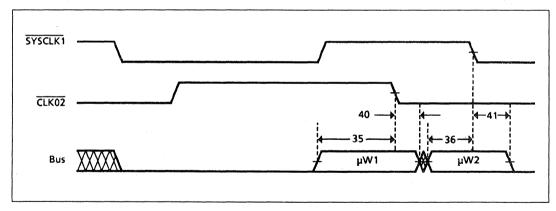

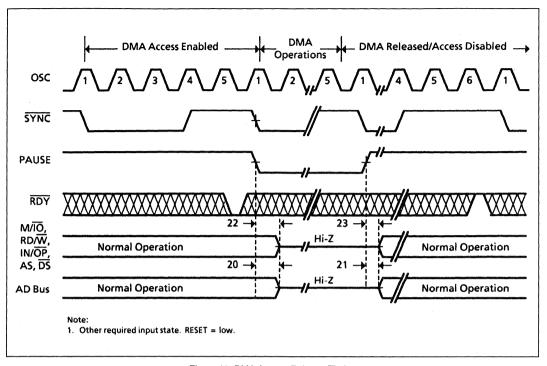

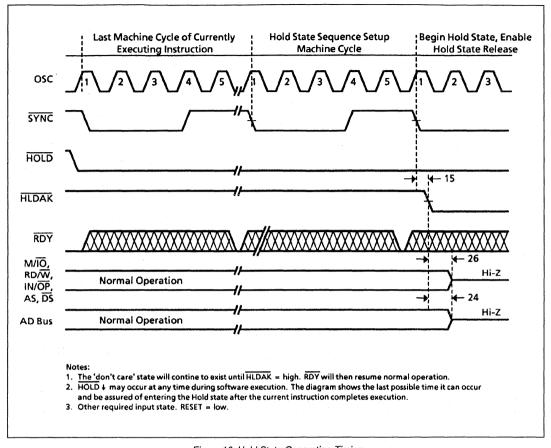

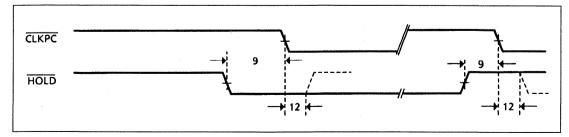

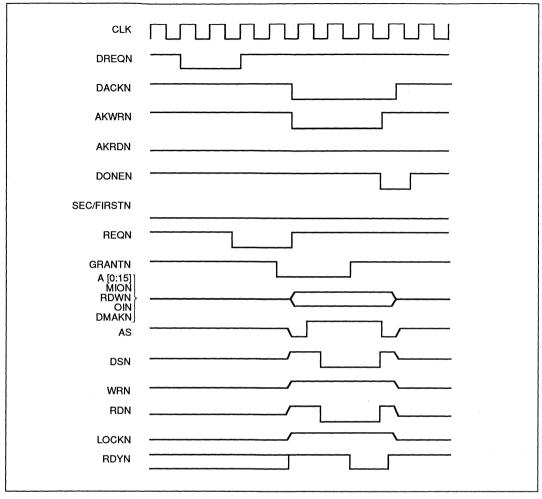

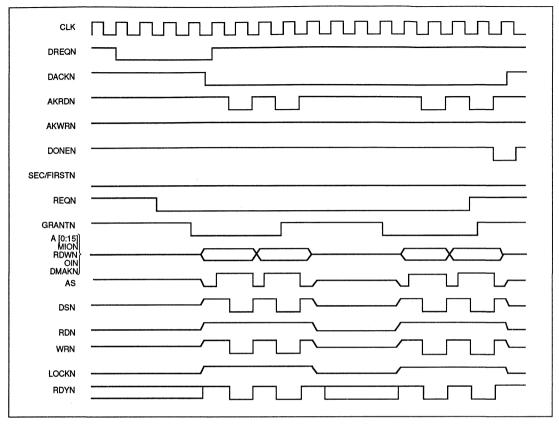

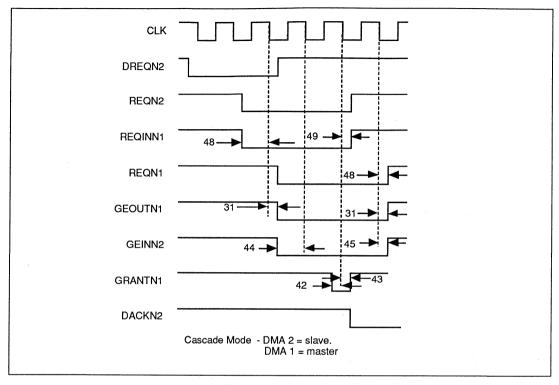

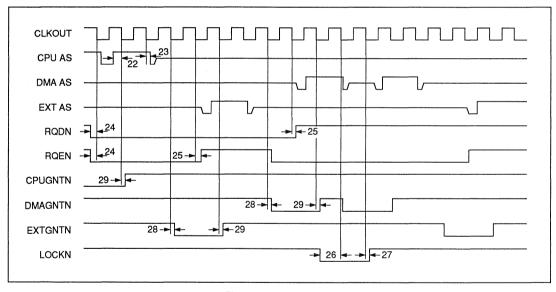

Once initialisation has been completed, the processor will begin instruction execution by executing a sequence of micro-instructions, each one machine cycle (two system clock periods) long. Each machine cycle may perform either an internal or an external operation; if the operation is purely internal then the system busses will not be in use and may be reassigned to another processor.

An external machine cycle (indicated by REQN low during the second half of the previous cycle) will cause the processor to stall upon completion of the current microcycle, awaiting GRANTN asserted low. Whilst GRANTN is high the busses remain undriven.

In simple, single processor systems which use no DMA devices the GRANTN line should be tied to GND to allow the processor to retain control of the busses. The LOCKN and REQN pins can be left open-circuit in this case. Applications Note 11 provides further information for designers of systems with more than one bus master.

#### 4. SOFTWARE CONSIDERATIONS

#### 4.1. OPERATING MODES

The MA31750 is capable of being operated in one of two basic modes as previously mentioned. These are described in detail below:

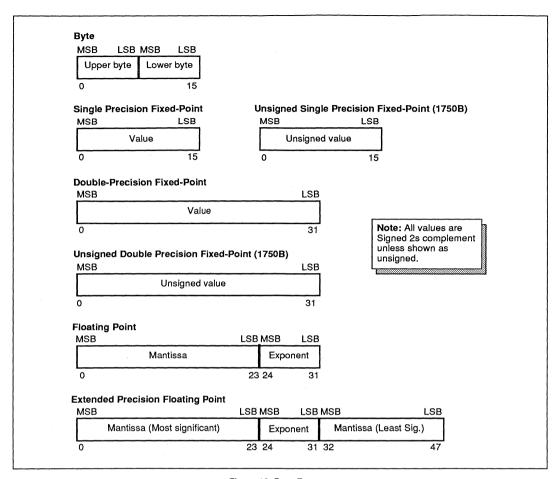

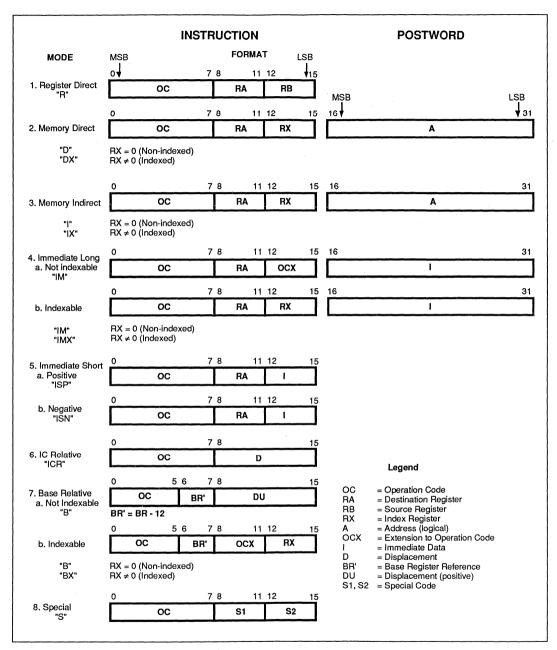

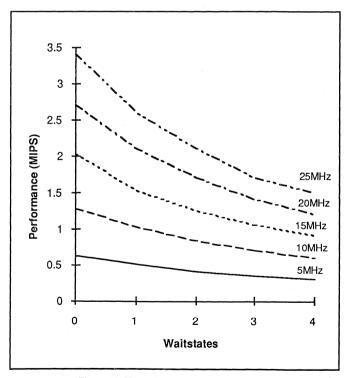

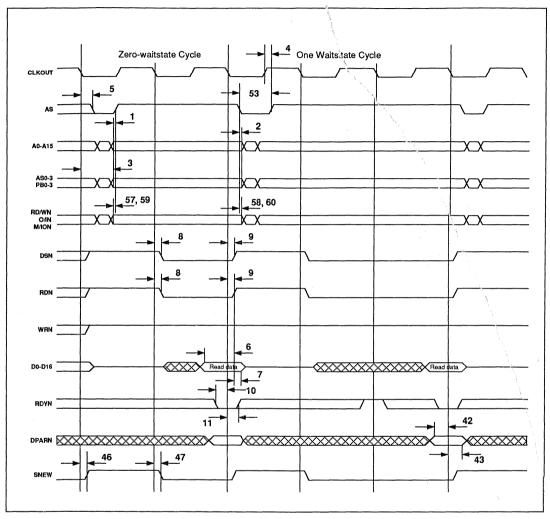

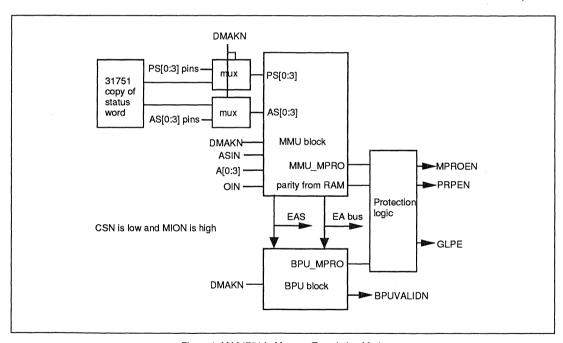

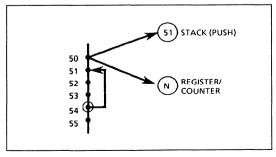

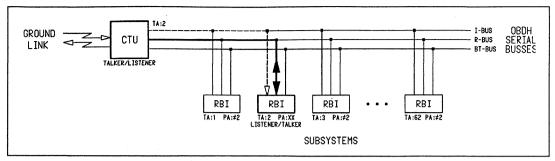

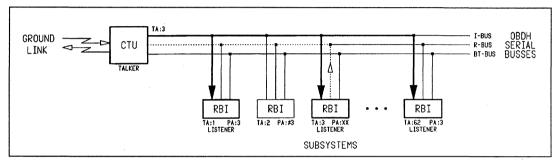

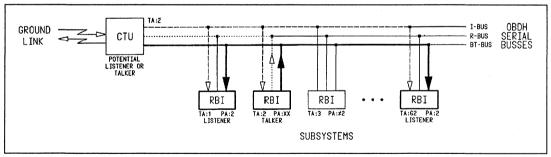

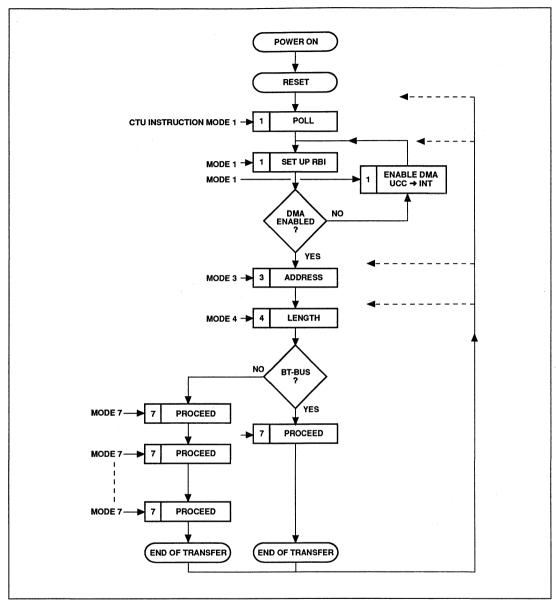

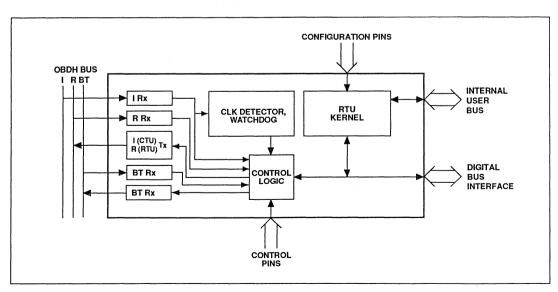

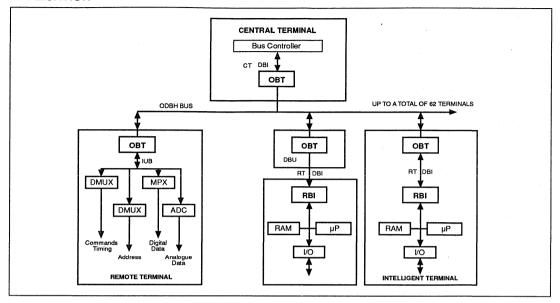

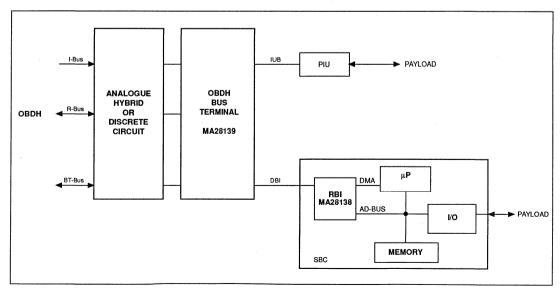

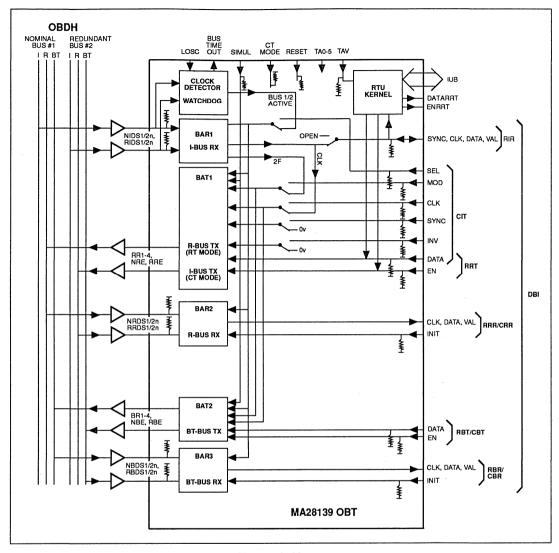

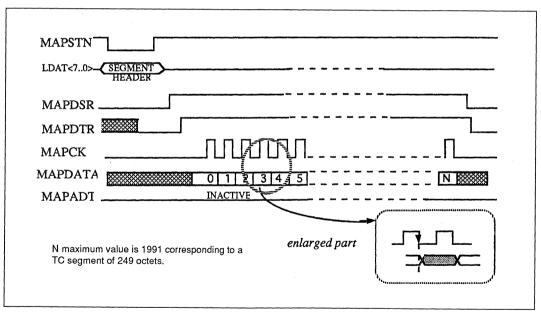

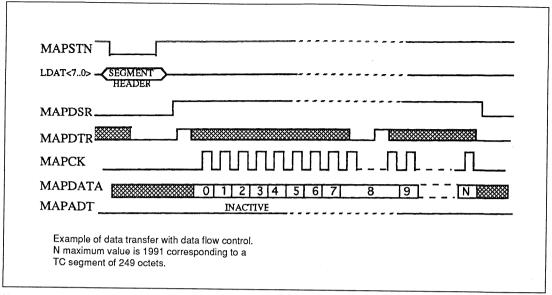

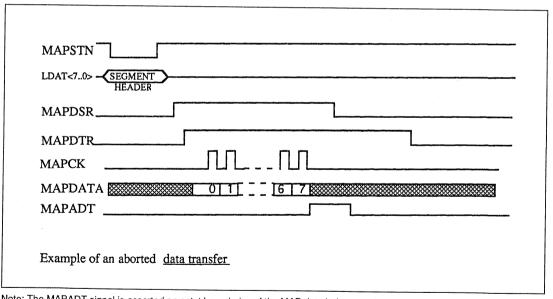

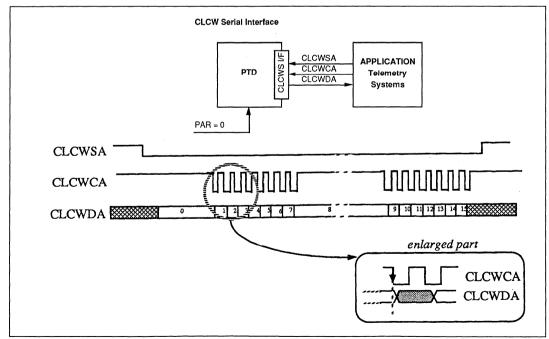

#### 4.1.1 1750A MODE